# UM10606 BGA7350 performance at IF=172.2 MHz Rev. 1 — 14 November 2012

**User manual**

### **Document information**

| Info     | Content                                                                                                                                |

|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | Dual VGA. 28 dB attenuator range IF=172.2 MHz NXP                                                                                      |

| Abstract | This User Manual describes the functionality and performance of the single ended BGA7350 evaluation board, tuned for a IF of 172.2 MHz |

### BGA7350 performance at IF=172.2 MHz

### **Revision history**

| Rev | Date     | Description       |

|-----|----------|-------------------|

| 1   | 20121114 | First publication |

# **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

### BGA7350 performance at IF=172.2 MHz

### 1. Introduction

The BGA7350 is a Silicon MMIC (Monolithic Microwave Integrated Circuit) processed in NXP's mainstream Si QuBIC4+ BiCmos process. This process intrinsic inhibits high  $F_T$  figures (up to 28 GHz), while not compromising ruggedness (breakdown voltage) and noise figures. These characteristics make this device suitable for versatile IF applications like in Base station receive path. The BGA7350 exhibits a logic-level shutdown control to reduce supply current. The BGA7350 is packed in the leadless HVQFN (5 x 5 mm²), and in combination with the optimized die design, gives excellent thermal performance,

To ensure optimal ESD protections, all pins are ESD protected.

All above mentioned highlight makes the BGA7350 and extreme attractive device with optimal performance/cost ratio, as compared to other devices in the market.

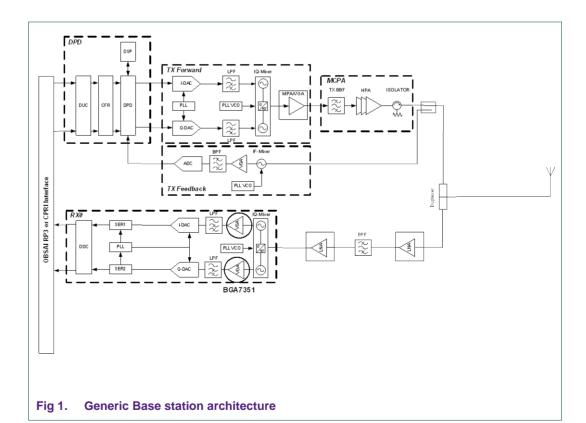

The single ended 172.2 MHz evaluation board (EVB) is designed for optimal performance in the 172.2 MHz frequency ranges, with a bandwidth of 28 MHz, suitable for base station Rx applications, as shown in Fig. 1.

BGA7350 performance at IF=172.2 MHz

### 2. Product Profile

### 2.1 General description

The BGA7350 MMIC is a dual independently digitally controlled IF Variable Gain Amplifier (VGA) operating from 50 MHz to 250 MHz Each IF VGA amplifies with a gain range of 24 dB and at its maximum gain setting delivers 17 dBm output power at 1 dB gain compression and a superior linear performance.

The BGA7350 Dual IF VGA is optimized for a differential gain error of less than  $\pm 0.1$  dB for accurate gain control and has a total integrated gain error of less than  $\pm 0.3$  dB.

The gain controls of each amplifier are separate digital gain-control word, which is provided externally through two sets of 5 bits.

The BGA7350 is housed in a 32 pins  $5 \times 5$  mm2 leadless HVQFN package.

### 2.2 Features and benefits

- Dual independent digitally controlled 28 dB gain range VGAs, with 5-bit control interface

- 50 MHz to 250 MHz frequency operating range

- Gain step size: 1 dB ± 0.1 dB

- 18.5 dB small signal gain

- Fast gain stage switching capability

- 17 dBm output power at 1 dB gain compression

- 5 V single supply operation with power-down control

- Logic-level shutdown control pin reduces supply current

- Excellent ESD protection at all pins

- Moisture sensitivity level 2

- Compliant to Directive 2002/95/EC, regarding Restriction of Hazardous Substances (RoHS)

- Unconditionally stable

- Excellent differential and integrated gain error

### 2.3 Applications

- Compatible with GSM / W-CDMA carrier/ WiMAX / LTE base-station infrastructure / multi systems carrier

- Multi channel receivers

- General use for DAC driver applications

BGA7350 performance at IF=172.2 MHz

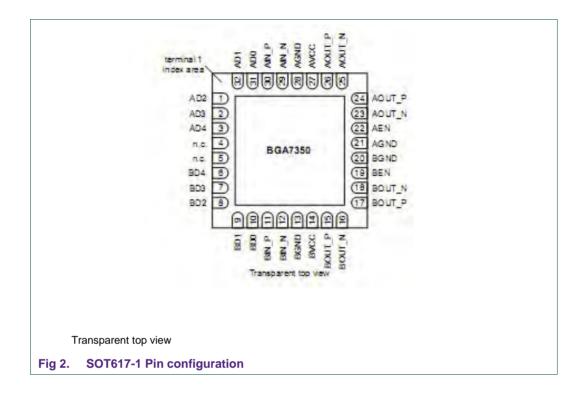

# 3. Pinning information

### BGA7350 performance at IF=172.2 MHz

# 3.1 Pin description

Table 2. Pin description

| Table 2.         | Pin description |                                                 |

|------------------|-----------------|-------------------------------------------------|

| Symbol           | Pin             | Description                                     |

| AD2              | 1               | MSB – 2 for gain control interface of channel A |

| AD3              | 2               | MSB – 1 for gain control interface of channel A |

| AD4              | 3               | MSB for gain control interface of channel A     |

| n.c.             | 4               | not connected [1]                               |

| n.c.             | 5               | not connected [1]                               |

| BD4              | 6               | MSB for gain control interface of channel B     |

| BD3              | 7               | MSB – 1 for gain control interface of channel B |

| BD2              | 8               | MSB – 2 for gain control interface of channel B |

| BD1              | 9               | LSB + 1 for gain control interface of channel B |

| BD0              | 10              | LSB for gain control interface of channel B     |

| BIN_P            | 11              | channel B positive input [2]                    |

| BIN_N            | 12              | channel B negative input [2]                    |

| GNDB             | 13, 20          | ground for channel B                            |

| V <sub>CCB</sub> | 14              | supply voltage for channel B 3                  |

| BOUT_P           | 15, 17          | channel B positive output [2]                   |

| BOUT_N           | 16, 18          | channel B negative output [2]                   |

| BEN              | 19              | power enable pin for channel B                  |

| GNDA             | 21, 28          | ground for channel A                            |

| AEN              | 22              | power enable pin for channel A                  |

| AOUT_N           | 23, 25          | channel A negative output [2]                   |

| AOUT_P           | 24, 26          | channel A positive output [2]                   |

| VCCA             | 27              | supply voltage for channel A [3]                |

| AIN_N            | 29              | channel A negative input [2]                    |

| AIN_P            | 30              | channel A positive input [2]                    |

| AD0              | 31              | LSB for gain control interface of channel A     |

| AD1              | 32              | LSB + 1 for gain control interface of channel A |

| GND              | GND paddle      | RF ground and DC ground [4]                     |

<sup>[1]</sup> Pin to be left open.

<sup>[2]</sup> Each channel should be independently enabled with logic HIGH and disabled with logic LOW.

<sup>[3]</sup> RF decoupled.

<sup>[4]</sup> The center metal base of the SOT617-1 also functions as heatsink for the VGA.

**UM10606 NXP Semiconductors**

BGA7350 performance at IF=172.2 MHz

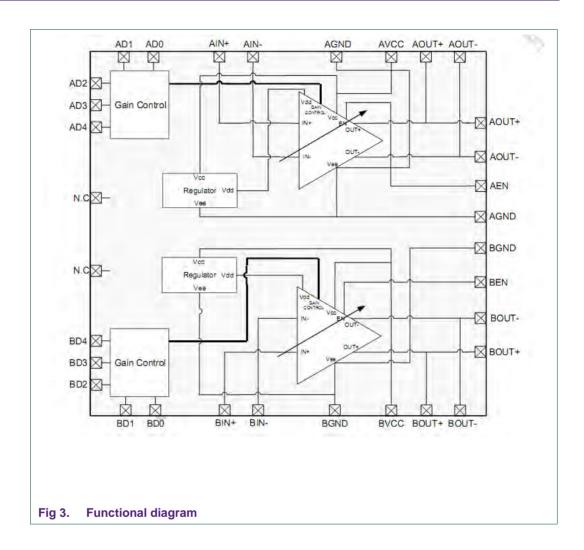

# **Functional Diagram**

# BGA7350 performance at IF=172.2 MHz

# 5. Gain control Range

| Input to all 0 to 4 gain control pins | nominal power gain [dB] |

|---------------------------------------|-------------------------|

| 00000                                 | 22                      |

| 00001                                 | 21                      |

| 00010                                 | 20                      |

| 00011                                 | 19                      |

| 00100                                 | 18                      |

| 00101                                 | 17                      |

| 00110                                 | 16                      |

| 00111                                 | 15                      |

| 01000                                 | 14                      |

| 01001                                 | 13                      |

| 01010                                 | 12                      |

| 01011                                 | 11                      |

| 01100                                 | 10                      |

| 01101                                 | 9                       |

| 01110                                 | 8                       |

| 01111                                 | 7                       |

| 10000                                 | 6                       |

| 10001                                 | 5                       |

| 10010                                 | 4                       |

| 10011                                 | 3                       |

| 10100                                 | 2                       |

| 10101                                 | 1                       |

| 10110                                 | 0                       |

| 10111                                 | -1                      |

| 11000                                 | -2                      |

| 11001                                 | -3                      |

| 11010                                 | -4                      |

| 11011                                 | <b>-</b> 5              |

| 11100                                 | -6                      |

| > 11100                               | -6                      |

Table 3 Gain control range

### BGA7350 performance at IF=172.2 MHz

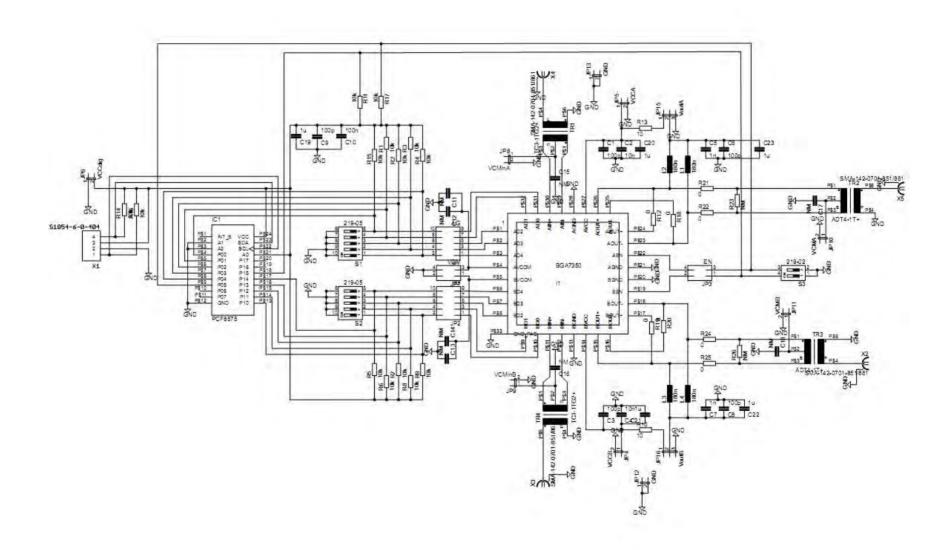

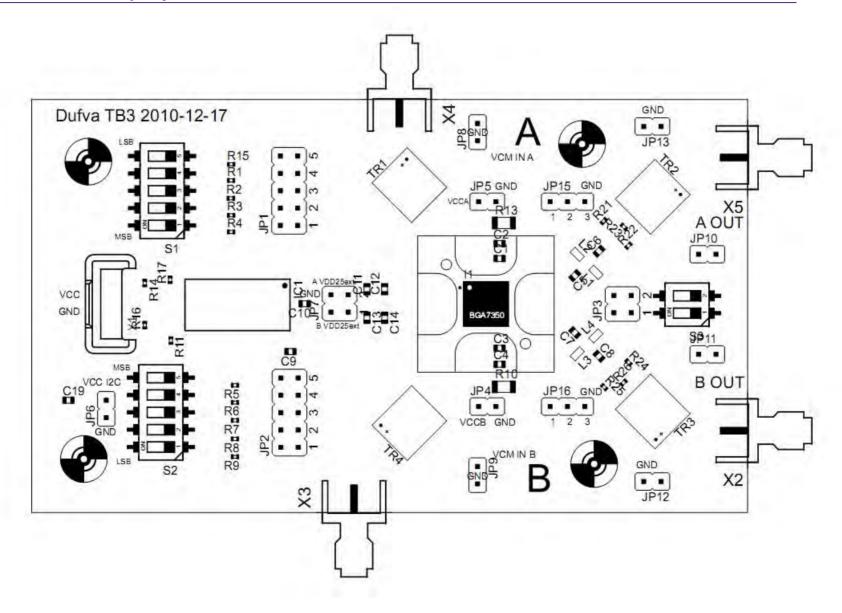

# 6. EVB circuit diagram

### BGA7350 performance at IF=172.2 MHz

# 7. Evaluation Board top layout

**UM10606 NXP Semiconductors**

### BGA7350 performance at IF=172.2 MHz

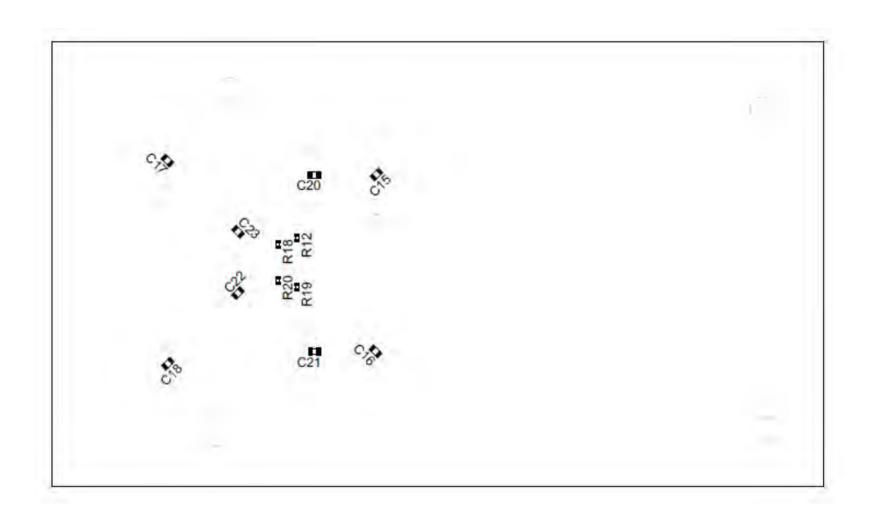

# 8. Evaluation board bottom layout

**User manual**

11 of 39

# BGA7350 performance at IF=172.2 MHz

# 9. Bill of Materials (BOM)

| Part       | Value        | Device    | Package  | Description |

|------------|--------------|-----------|----------|-------------|

| C1         | 100p         |           | C0603    | CAPACITOR   |

| C2         | 10n          |           | C0603    | CAPACITOR   |

| C3         | 100p         |           | C0603    | CAPACITOR   |

| C4         | 10n          |           | C0603    | CAPACITOR   |

| C5         | 1n           |           | C0603    | CAPACITOR   |

| C6         | 100p         |           | C0603    | CAPACITOR   |

| C7         | 1n           |           | C0603    | CAPACITOR   |

| C8         | 100p         |           | C0603    | CAPACITOR   |

| C9         | 100p         |           | C0603    | CAPACITOR   |

| C10        | 100n         |           | C0603    | CAPACITOR   |

| C11        | NM           |           | C0603    | CAPACITOR   |

| C12        | NM           |           | C0603    | CAPACITOR   |

| C13        | NM           |           | C0603    | CAPACITOR   |

| C14        | NM           |           | C0603    | CAPACITOR   |

| C15        | 100n         |           | C0603    | CAPACITOR   |

| C16        | 100n         |           | C0603    | CAPACITOR   |

| C17        | 100n<br>100n |           | C0603    | CAPACITOR   |

| C17<br>C18 | 100n<br>100n |           | C0603    | CAPACITOR   |

| C18        |              |           |          | CAPACITOR   |

| C20        | 100n         |           | C0603    |             |

|            | 100n         |           | C0603    | CAPACITOR   |

| C25        | 1u           |           | C0603    | CAPACITOR   |

| C26        | 1u           |           | C0603    | CAPACITOR   |

| C27        | 1u           |           | C0603    | CAPACITOR   |

| C28        | 1u           |           | C0603    | CAPACITOR   |

| C29        | 1u           |           | C0603    | CAPACITOR   |

| I1         | BGA7350      |           | SOT617-1 | BGA7350     |

| ID4        | 4.0          | 0.5:      | IDS      | III MDED    |

| JP1        | AG           | 2 x 5pins | JP5      | JUMPER      |

| JP2        | BG           | 2 x 5pins | JP5      | JUMPER      |

| JP3        | EN           | 2 x 2pins | JP2      | JUMPER      |

| JP4        | VCCB         | 1 x2pins  | JP1      | JUMPER      |

| JP5        | VCCA         | 1 x2pins  | JP1      | JUMPER      |

| JP6        | VCCdig       | 1 x2pins  | JP1      | JUMPER      |

| JP7        | VCM          | 2 x 2pins | JP2      | JUMPER      |

| JP8        | VCMinA       | 1 x2pins  | JP1      | JUMPER      |

| JP9        | VCMinB       | 1 x2pins  | JP1      | JUMPER      |

| JP10       | VCMA         | 1 x2pins  | JP1      | JUMPER      |

| JP11       | VCMB         | 1 x2pins  | JP1      | JUMPER      |

| JP12       | GND          | 1 x2pins  | JP1      | JUMPER      |

| JP13       | GND          | 1 x2pins  | JP1      | JUMPER      |

| JP15       | VoutA        | 1 x3pins  | JP3      | JUMPER      |

| JP16       | VoutB        | 1 x3pins  | JP3      | JUMPER      |

| 1.4        | 400-         | 00001.0   | 00001.0  |             |

| L1         | 100n         | 0603LS    | 0603LS   |             |

| L2         | 100n         | 0603LS    | 0603LS   |             |

| L3         | 100n         | 0603LS    | 0603LS   |             |

| L4         | 100n         | 0603LS    | 0603LS   |             |

|            |              |           |          |             |

# BGA7350 performance at IF=172.2 MHz

| Part                                                                                                                             | Value                                                    | Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part  R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11 R12 R13 R14 R15 R16 R17 R18 R20 R21 R22 R23 R24 R25 R26 R27 R28 R29 R30 R31 R32 R33 R34 | Value  10k 10k 10k 10k 10k 10k 10k 10k 10 10k 10 10k 10k | R-EU_R0402 | R0402 R1206 R0402 | RESISTOR |

| R37<br>R38<br>S1<br>S2<br>S3                                                                                                     | NM<br>0<br>DIP<br>DIP<br>DIP                             | R-EU_R0402<br>R-EU_R0402<br>219-05<br>219-05<br>219-02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R0402<br>R0402<br>CTS-219-05<br>CTS-219-05<br>CTS-219-02                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RESISTOR<br>RESISTOR<br>Surface<br>Surface<br>Surface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TR1<br>TR2<br>TR3<br>TR9                                                                                                         | ADT3-1T+<br>ADT4-1T+<br>ADT4-1T+<br>ADT3-1T+             | transformer<br>transformer<br>transformer<br>transformer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Mini-Circuits<br>Mini-Circuits<br>Mini-Circuits<br>Mini-Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| X1<br>X2<br>X3<br>X4<br>X5<br>X10<br>X11<br>X12<br>X13<br>X14                                                                    | NM BOUT_P BIN_P AIN_P AOUT_P NM NM NM NM NM NM           | con SMA connector SMA connector SMA connector SMA connector BU-SMA-V SMA connector SMA connector SMA connector SMA connector SMA connector SMA connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SMA<br>SMA<br>SMA<br>SMA<br>FEMALE<br>SMA<br>SMA<br>SMA<br>FEMALE<br>SMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

**UM10606 NXP Semiconductors**

BGA7350 performance at IF=172.2 MHz

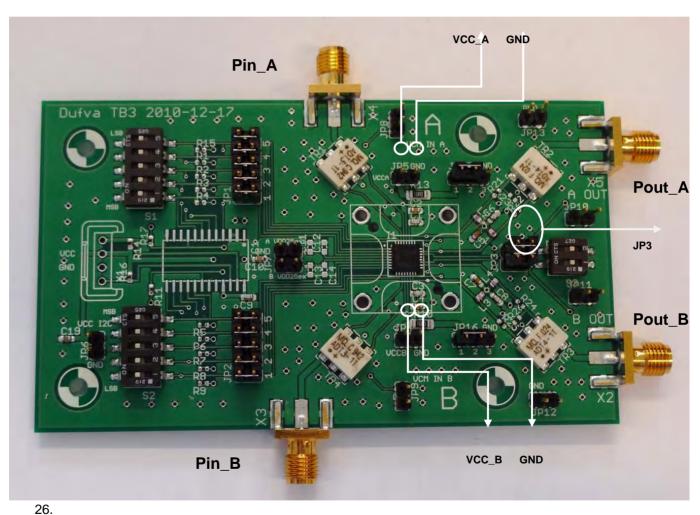

# 10. Operation of the BGA7350 EVB

# 10.1 Applying bias

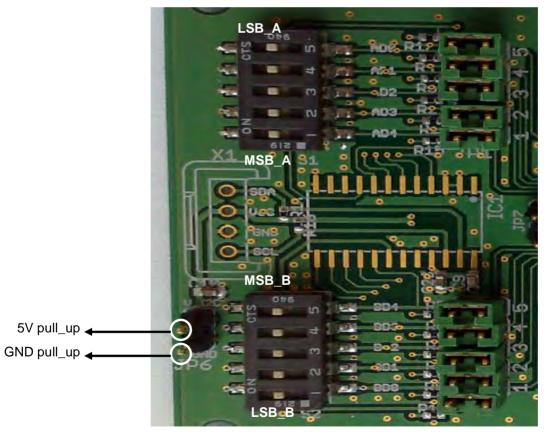

The EVB, as shown in Fig. 4, should be connected to 5V supply, according the following connections:

- 1. Leave jumpers JP3 in their current position, as shown in Fig. 4

- 2. Apply +5V to VCC\_A and/or VCC\_B to the pins, as shown in Fig. 4

- 3. Apply ground to GND\_A and/or GND\_B pins

Fig 4. BGA7350 EVB picture

### BGA7350 performance at IF=172.2 MHz

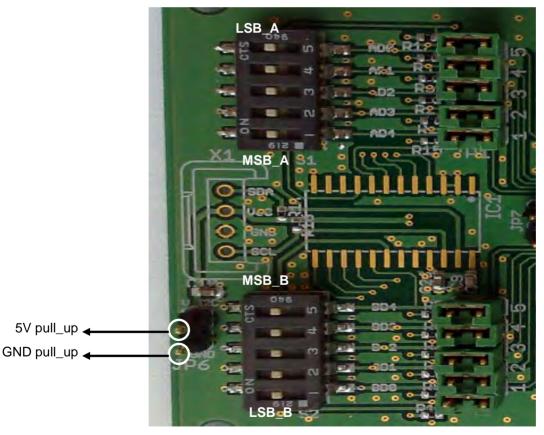

### 10.2 Mode of operation

The EVB of the BGA7350 can either be operated in the manual mode or 'automatic' mode. The BGA7350 can be enabled/disabled by switch3 (see Fig.5)

Fig 5. Enable/disable switch S3

### 10.2.1 Manual mode.

For manual mode operation, all jumpers, as shown in Fig. 5 must be in place. Also a 5V pull-up voltage and ground should be applied, as indicated as 5V/GND pull-up in Fig. 6.

Fig. 6 Manual gain settings by switches S1 and S2

With the positions of S1 and S2, the gain range can be adjusted according the values in Table.3.

### BGA7350 performance at IF=172.2 MHz

### 10.3 Mode of operation

The EVB of the BGA7350 can either be operated in the manual mode or 'automatic' mode. The BGA7350 can be enabled/disabled by switch3 (see Fig.5)

Fig 5. Enable/disable switch S3

### 10.3.1 Manual mode.

For manual mode operation, all jumpers, as shown in Fig. 5 must be in place. Also a 5V pull-up voltage and ground should be applied, as indicated as 5V/GND pull-up in Fig. 6.

Fig. 6 Manual gain settings by switches S1 and S2

With the positions of S1 and S2, the gain range can be adjusted according the values in Table.3.

### BGA7350 performance at IF=172.2 MHz

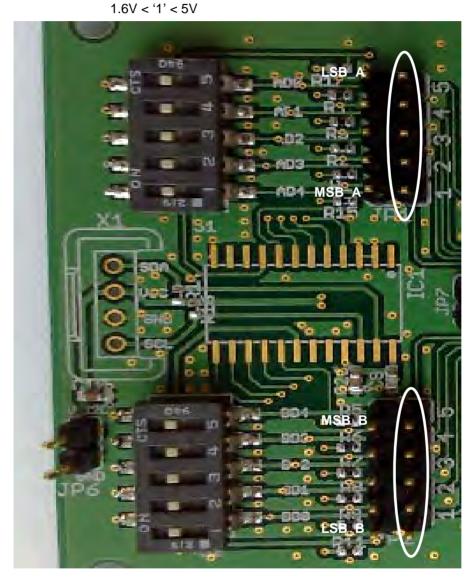

### 10.3.2 'Automatic' mode

For 'automatic' mode of operations the jumpers according Fig. 6 should be removed, and logic levels should be applied to the rows (also I<sup>2</sup>C operation is possible, but not functional on this EVB), as indicated by the white circles (see Fig. 7). The logic levels applied to the pins should be within the following range:

0V < '0' < 0.8V

Fig. 7 Gain setting control by logic levels, according table 3

### BGA7350 performance at IF=172.2 MHz

# 11. Measurements

On the BGA7350, the following measurements have been performed:

1. S-parameters. From the S-parameter measurements the following data can be deducted:

| a. | S-parameters                    | (Spar)                    |

|----|---------------------------------|---------------------------|

| b. | Power gain                      | $(G_p)$                   |

| c. | Gain adjustment range           | $(\Delta g_{\text{adj}})$ |

| d. | Gain step                       | $(G_{\text{step}})$       |

| e. | Gain Flatness                   | $(G_{\text{flat}})$       |

| f. | Differential gain error         | $(Eg_{\text{diff}})$      |

| g. | Integrated gain error           | $(Eg_{itg})$              |

| h. | Isolation                       | (ISL)                     |

| i. | Output power at 1dB compression | $(P_{1dB})$               |

2. Harmonic Measurements. From the Harmonic measurements the following data can be deducted:

a. Output third order intercept point (IP3<sub>0</sub>)

b. Second harmonic (H<sub>2</sub>)

- 3. Noise Measurements. From the Noise measurements the following data can be deducted:

- a. Noise Figure (NF)

- 4. Timing measurement. From the Timing measurements the following data can be deducted:

- a. Gain step settling time (min/max) (t<sub>s(step)G</sub>)

### BGA7350 performance at IF=172.2 MHz

### 11.1 Measurement definitions

### 11.1.1 Differential input and output impedance

```

|Zi| = |((1+S_{11}(F)) / (1-S_{11}(F)))| * 500hm, with F = 100MHz ... 240MHz |Zo| = |((1+S_{22}(F)) / (1-S_{22}(F)))| * 500hm, with F = 100MHz ... 240MHz

```

### 11.1.2 Absolute gain accuracy

Absolute gain accuracy  $(170\text{Mhz}) = 20\log(|S_{21}(170\text{MHz})|) - 22\text{dB}$  (=typical max gain)

### 11.1.3 Gain flatness

```

Gain flatness (F) = Max (Gain(F + \frac{1}{2} Fd ... F - \frac{1}{2} Fd)) – Min (Gain(F + \frac{1}{2} Fd ... F - \frac{1}{2} Fd)) with Gain(F) = 20*\log(|S_{21}(F)|)

```

### 11.1.4 Differential gain errors

```

Differential gain error = max | Gain(x) – Gain(x-1) – 1dB |, with Gain(x) = 20log(|S_{21}(x)|) measured at 170 MHz and x = gain setting (1...24)

```

Differential gain error (upper 12dB) =

$$| Gain(0) - Gain(12) - 12dB |$$

, with  $Gain(x) = 20log(|S_{21}(x)|)$  measured at 170 MHz and x = gain setting

```

Differential gain error (full range) = | Gain(0) - Gain(24) - 24dB |, with Gain(x) = 20log(|S_{21}(x)|) measured at 170 MHz and x = gain setting

```

### 11.1.5 Differential phase errors

```

Differential phase error (consecutive gain steps) = arg(S_{21}(x)) - arg(S_{21}(x-1))

with x = gain setting (0...24), measured 170 MHz

```

```

Differential phase error (any two steps upper 12dB) = \max(\arg(S_{21}(x;x-12))) - \min(\arg(S_{21}(x;x-12)))

```

with x = gain setting, measured at 170 MHz

Differential phase error (any two steps) =  $max(arg(S_{21}(x))) - min(arg(S_{21}(x)))$ with x = gain setting (0...24), measured at 170 MHz

## BGA7350 performance at IF=172.2 MHz

### 11.1.6 OPI3

OIP3low = Po(

$$F_1$$

)+ ½ (Po( $F_1$ )-Po( $F_1$ -2MHz)), with  $F_1$ =170 MHz  $F_2$  =  $F_1$ +2MHz OIP3high = Po( $F_2$ )+ ½ (Po( $F_2$ )-Po( $F_2$ -2MHz)), with  $F_1$ =170 MHz  $F_2$  =  $F_1$ +2MHz OIP3 = Min (OIP3low, OIP3high)

### 11.1.7 H2

$$2^{nd}$$

order harm (F) =  $20log(|S21(2*F)|) - 20log((|S21(F)|)$

### BGA7350 performance at IF=172.2 MHz

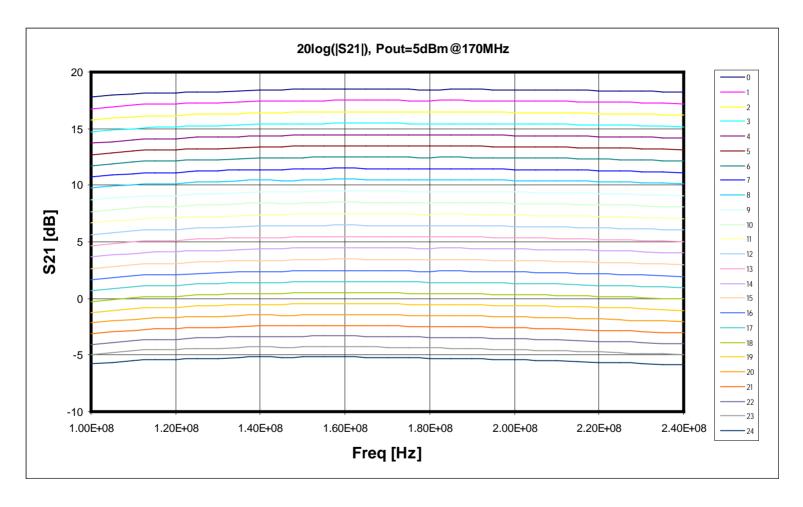

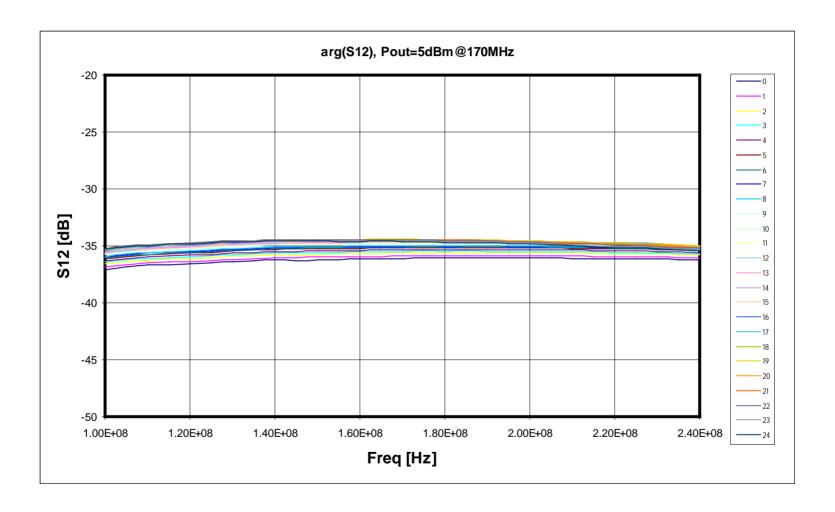

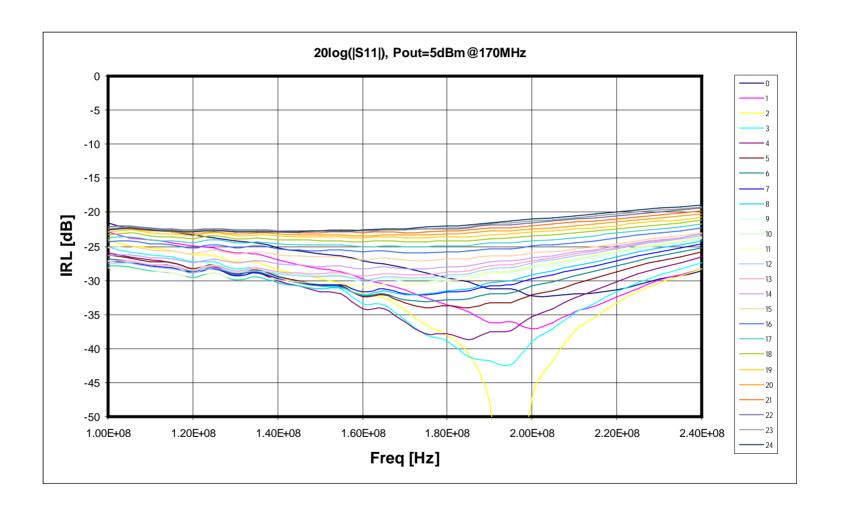

### 11.2 S-parameter measurements

The S-parameters (and the above mentioned derivative measurements) are measured with a full two-port calibrated network analyzer; over the frequency range 100-240 MHz. Also the output power compression point ( $P_{1dB}$ ) has been measured with the network analyzer. In the latter case, a calibrated power sweep has been performed, in order to obtain the  $P_{1dB}$ .

All gain and phase measurements have been performed with a constant output power of +5 dBm, meaning that for every 1 dB increase of attenuation, the input power also have to increase by +1 dBm.

The non-used port's of the dual VGA (channel A or B) has been terminated with a 50-Ohm load.

The isolation measurement (ISL) have been performed by injecting the signal to the input of channel A, and measuring the response at the output of channel B (and vice versa), with the remaining input and output terminated with 50 Ohm.

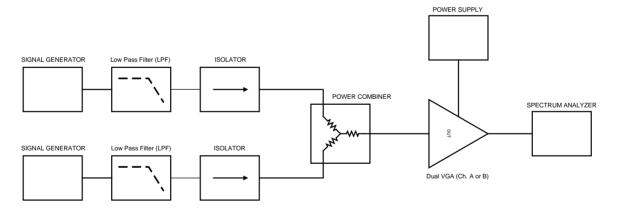

### 11.3 Harmonic measurements.

The harmonic measurements (OIP<sub>2</sub>, OIP<sub>3</sub> and H<sub>2</sub>) have been measured with a set-up, as described in Fig. 8.

Fig. 8 Harmonic measurement set-up

A low-pass filter at the output of the signal generators guaranties suppression of the  $H_2$  generated by the generator itself.

BGA7350 performance at IF=172.2 MHz

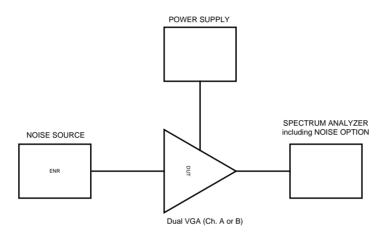

### 11.4 Noise Figure measurements

The Noise Figure (NF) has been measured with a noise source (Excess Noise Ratio ENR=15.3 dB), in combination with a spectrum analyzer with a noise measurement option. (See Fig.9)

Fig. 9 Noise Figure Measurements

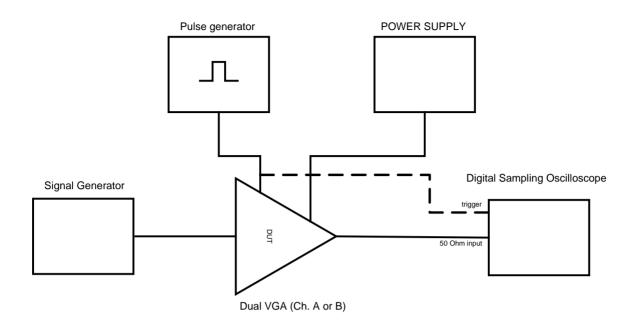

### 11.5 Timing Measurement.

In order to determine the gain step settling time, the set-up as shown in Fig. 10 has been used. A pulse generator (preferably a pulse generator that can supply the proper logic levels) is connected to the disable/enable pin of the EVB. The input (Pin\_A or Pin\_B) is connected to a signal generator (or network analyzer) to supply the RF input signal. The response (Pout\_A or Pout\_B) is measured with a digital sampling scope, triggered by the pulse generator. The 50-Ohm input of the sampling scope is used, in order to terminate the output of the dual VGA properly.

With the pulse generator, the gain settings are switch from minimum (00000) to maximum (11000) attenuation.

### BGA7350 performance at IF=172.2 MHz

Fig. 10 Timing measurements

### 11.6 Measurement results

The section following below shows performance measurements of the BGA7350 EVB in single-ended operations.

The EVB has been measured under the following conditions:

- Measurement data corrected for input-and output transformer losses

- Input transformer; losses 0.55 dB, transformer ratio 1:3

- Output transformer; losses 0.6 dB, transformer ratio 1:4

- EVB optimized for 172.2 MHz operation (other frequency ranges can be easily optimized by changing L1 .. L4, see also circuit diagram.

- 5V supply

- 25 deg. Ambient temperature

### BGA7350 performance at IF=172.2 MHz

# 11.6.1 Gain as function of frequency and attenuator range

Note: every gain step measured @Pout= 5dBm

### BGA7350 performance at IF=172.2 MHz

11.6.2 S-parameters; S12

Note: every gain step measured @Pout= 5dBm

### BGA7350 performance at IF=172.2 MHz

11.6.3 S-parameters; S11

Note: every gain step measured @Pout= 5dBm

### BGA7350 performance at IF=172.2 MHz

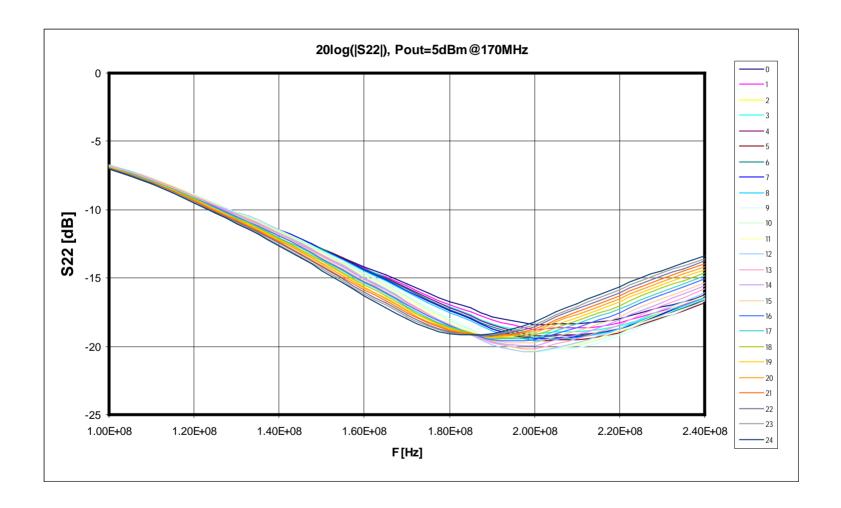

11.6.4 S-parameters; S22

Note: every gain step measured @Pout= 5dBm

### BGA7350 performance at IF=172.2 MHz

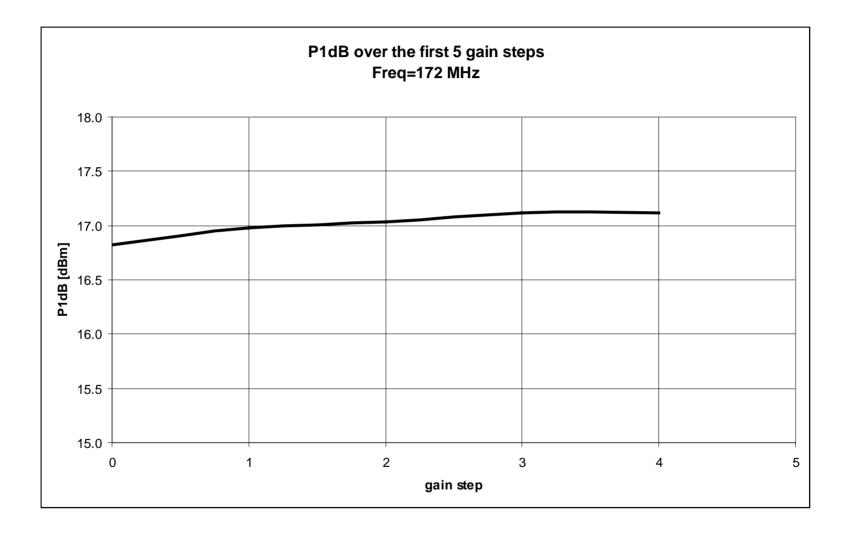

# 11.6.5 P1dB over first 5 gain steps

BGA7350 performance at IF=172.2 MHz

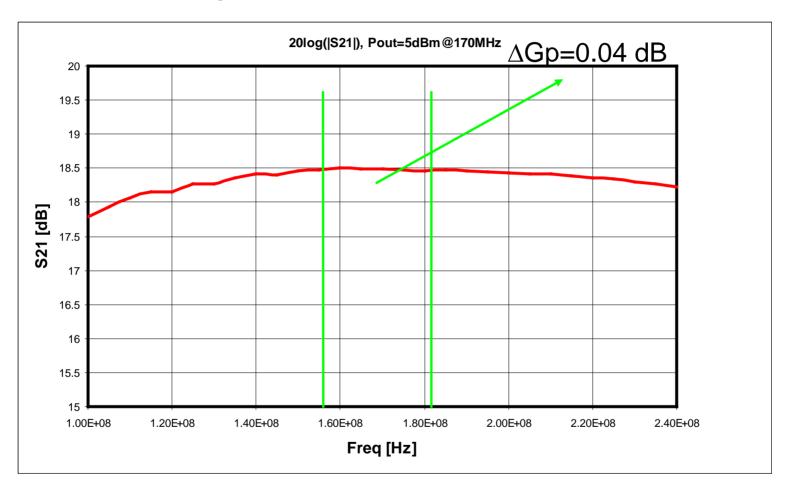

11.6.6 Gain Flatness @maximum gain

△Gp=0.04 dB over operating frequency band

BGA7350 performance at IF=172.2 MHz

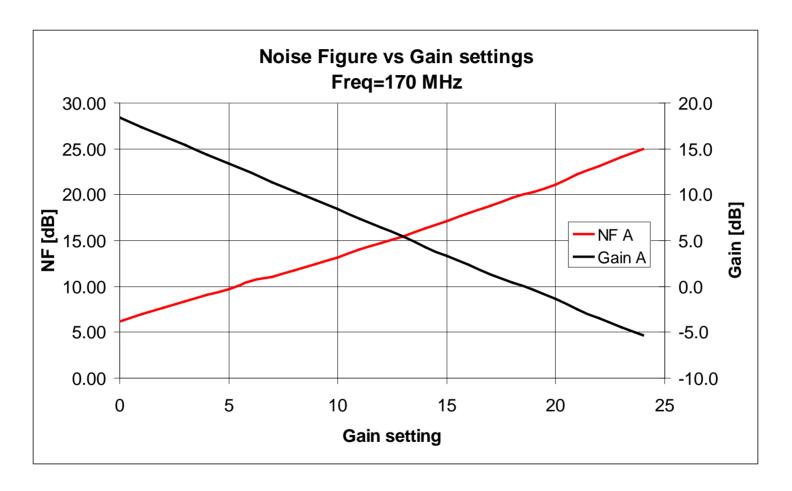

### 11.6.7 Noise Figure versus gain settings

Fmin=6.2 dB (@minimum attenuation, noise step = 0.8dB/dB

### BGA7350 performance at IF=172.2 MHz

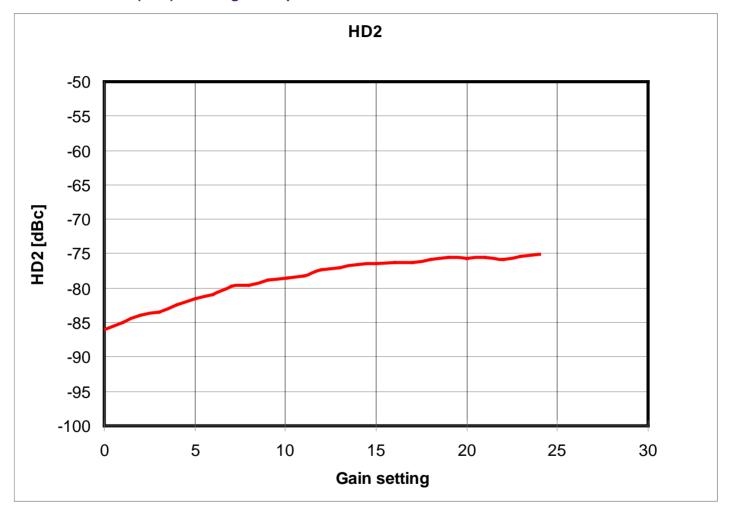

11.6.8 Harmonic Distortion (HD2) versus gain steps

Note: Pout=+5 dBm for every gain step

Freq\_in=86 MHz

### BGA7350 performance at IF=172.2 MHz

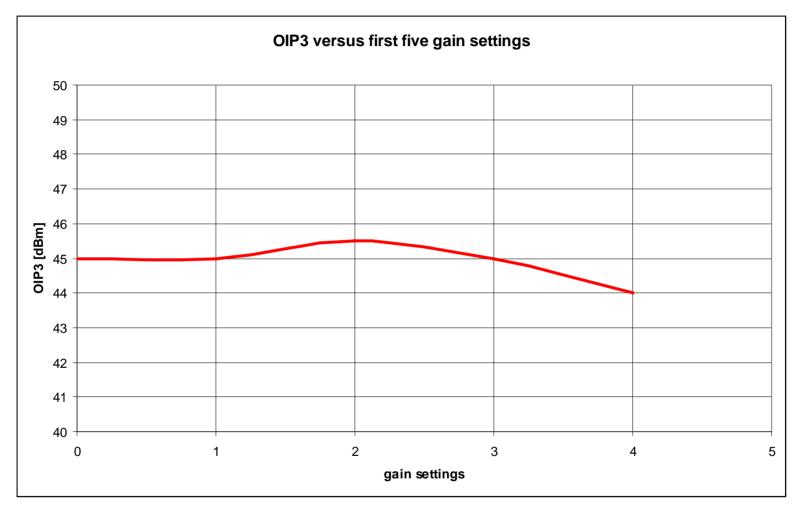

# 11.6.9 OIP3 over first 5 gain steps

Note: Pout per tone =+2 dBm Freq1=170 MHz; Freq2= 172 MHz

### BGA7350 performance at IF=172.2 MHz

# 11.6.10 Summary of the gain errors

| Measurement                                        | Unit | Value  | Conditions                                              |

|----------------------------------------------------|------|--------|---------------------------------------------------------|

| Temperature                                        | С    | 25 deg |                                                         |

| Power supply voltage                               | V    | 5      | Definition (incl cable loss)                            |

| Power supply current                               | mΑ   | 119.7  | Maximum supply current for all gain steps               |

| Standby current                                    | mΑ   | 2.45   | Maximum standby current (for all gain steps)            |

| Absolute gain                                      | dB   | 18.50  | Gain measured at F=170MHz, imcluding transformer losses |

| Differential gain error per 1dB consecutive steps  | [dB] | 0.10   | Measured at F=170MHz                                    |

| Integrated gain error upper 12dB                   | dB   | 0.04   | Measured at F=170MHz                                    |

| Integrated gain error full range                   | dB   | -0.28  | Measured at F=170MHz                                    |

| Gain flatness over 30MHz bandwidth at maximum gain | dB   | 0.04   | pk-pk over 30MHz bandwidth at gain=0                    |

| Gain flatness over 30MHz bandwidth at minimum gain | dB   | 0.14   | pk-pk over 30MHz bandwidth at gain=24                   |

| Maximum gain flatness over 30MHz                   | dB   | 0.04   | Maximum flatness over 30MHz for all gain steps          |

| Minimum gain flatness over 30MHz                   | dB   | 0.16   | Minimum flatness over 30MHz for all gain steps          |

### 11.6.11 Isolation (between channel A and channel B)

| Gain settings @170 MHz | isolation [dB] |

|------------------------|----------------|

| min                    | -59.8          |

| max                    | -60            |

Measured @Pout=5dBm for both min and max gain

# 11.6.12 Impedance summary

| Measurement                                    | Unit | Value | Conditions                                                               |

|------------------------------------------------|------|-------|--------------------------------------------------------------------------|

| Maximum input impedance (BW=30 all gainsteps)  | Ohm  | 54.5  | Maximum absolute value measured over 30MHz bandwidth, for all gain steps |

| Minimum input impedance (BW=30 all gainsteps)  | Ohm  | 42.6  | Minimum absolute value measured over 30MHz bandwidth, for all gain steps |

| Maximum output impedance (BW=30 all gainsteps) | Ohm  | 57.8  | Maximum absolute value measured over 30MHz bandwidth, for all gain steps |

| Minimum output impedance (BW=30 all gainsteps) | Ohm  | 47.0  | Minimum absolute value measured over 30MHz bandwidth, for all gain steps |

| Maximum input impedance (BW=30 all gainsteps)  | Ohm  | 54.5  | Maximum real value measured over 30MHz bandwidth, for all gain steps     |

| Minimum input impedance (BW=30 all gainsteps)  | Ohm  | 42.6  | Minimum real value measured over 30MHz bandwidth, for all gain steps     |

| Maximum output impedance (BW=30 all gainsteps) | Ohm  | 53.7  | Maximum real value measured over 30MHz bandwidth, for all gain steps     |

| Minimum output impedance (BW=30 all gainsteps) | Ohm  | 46.0  | Minimum real value measured over 30MHz bandwidth, for all gain steps     |

### BGA7350 performance at IF=172.2 MHz

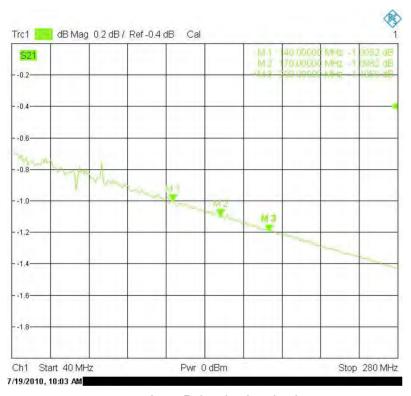

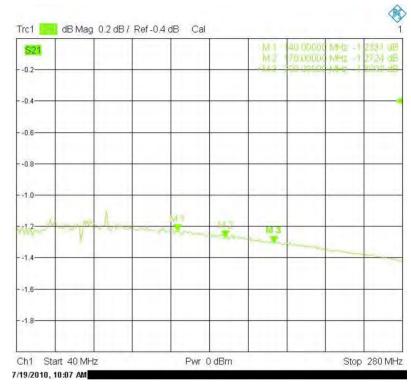

### 12. Balun Characterization

In order to determine the BGA7350 performance only, the input-and output balun characteristics (losses) must be determined for correction. This has been done by measuring the baluns (both input and output) back-to-back, and assuming that both transformers are identical, the measured losses can be divided by two, to determine the losses per balun.

The measurements have been performed on the (calibration) boards, as described below)

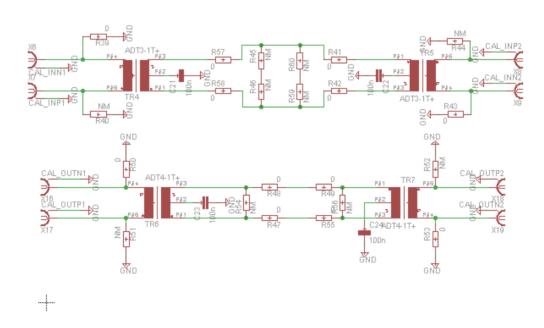

### 12.1 Calibration EVB schematics

BGA7350 performance at IF=172.2 MHz

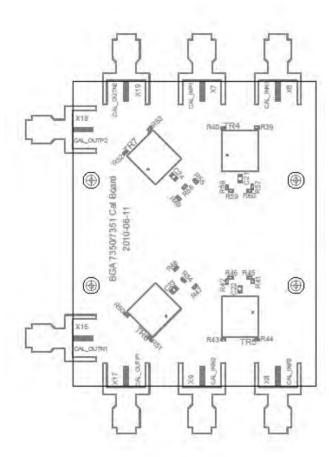

# 12.2 Calibration EVB layout

### BGA7350 performance at IF=172.2 MHz

# 12.3 Calibration EVB picture

### BGA7350 performance at IF=172.2 MHz

### 12.4 Calibration measurement results

Input Balun, back-to-back

The losses of the input balun is about 0.55 dB The losses of the output balun is about 0.6 dB

Output Balun, back-to back

### BGA7350 performance at IF=172.2 MHz

# 13. Legal information

### 13.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 13.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

### 13.3 Licenses

### Purchase of NXP <xxx> components

<License statement text>

### 13.4 Patents

Notice is herewith given that the subject device uses one or more of the following patents and that each of these patents may have corresponding patents in other jurisdictions.

<Patent ID> — owned by <Company name>

### 13.5 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

<Name> — is a trademark of NXP B.V.

# BGA7350 performance at IF=172.2 MHz

# 14. Contents

| 1.               | Introduction                                  | 3   |

|------------------|-----------------------------------------------|-----|

| 2.               | Product Profile                               | 4   |

| 2.1              | General description                           | 4   |

| 2.2              | Features and benefits                         | 4   |

| 2.3              | Applications                                  | 4   |

| 3.               | Pinning information                           | 5   |

| 3.1              | Pin description                               | 6   |

| 4.               | Functional Diagram                            | 7   |

| 5.               | Gain control Range                            | 8   |

| 6.               | EVB circuit diagram                           | 9   |

| 7.               | Evaluation Board top layout                   | .10 |

| 8.               | Evaluation board bottom layout                | .11 |

| 9.               | Bill of Materials (BOM)                       | .12 |

| 10.              | Operation of the BGA7350 EVB                  | .14 |

| 10.1             | Applying bias                                 | 14  |

| 10.2             | Mode of operation                             |     |

| 10.2.1           | Manual mode                                   | 15  |

| 10.3             | Mode of operation                             | 16  |

| 10.3.1           | Manual mode                                   | 16  |

| 10.3.2           | 'Automatic' mode                              | 17  |

| 11.              | Measurements                                  | .18 |

| 11.1             | Measurement definitions                       |     |

| 11.1.1           | Differential input and output impedance       | 19  |

| 11.1.2           | Absolute gain accuracy                        |     |

| 11.1.3           | Gain flatness                                 |     |

| 11.1.4           | Differential gain errors                      |     |

| 11.1.5           | Differential phase errors                     |     |

| 11.1.6           | OPI3                                          |     |

| 11.1.7           | H2                                            |     |

| 11.2             | S-parameter measurements                      |     |

| 11.3             | Harmonic measurements                         |     |

| 11.4             | Noise Figure measurements                     |     |

| 11.5             | Timing Measurement                            |     |

| 11.6             | Measurement results                           | 23  |

| 11.6.1           | Gain as function of frequency and attenuator  | 0.4 |

| 44.00            | range                                         |     |

| 11.6.2           | S-parameters; S12                             |     |

| 11.6.3           | S-parameters; S11                             |     |

| 11.6.4           | S-parameters; S22                             |     |

| 11.6.5           | P1dB over first 5 gain steps                  |     |

| 11.6.6<br>11.6.7 | Gain Flatness @maximum gain                   |     |

| 11.6.7           | Noise Figure versus gain settings             |     |

|                  | Harmonic Distortion (HD2) versus gain steps . |     |

| 11.6.9           | OIP3 over first 5 gain steps                  | 52  |

| 11.6.10 | Summary of the gain errors                  | 33 |

|---------|---------------------------------------------|----|

| 11.6.11 | Isolation (between channel A and channel B) | 33 |

| 11.6.12 | Impedance summary                           | 33 |

| 12.     | Balun Characterization                      | 34 |

| 12.1    | Calibration EVB schematics                  | 34 |

| 12.2    | Calibration EVB layout                      | 35 |

| 12.3    | Calibration EVB picture                     | 36 |

| 12.4    | Calibration measurement results             | 37 |

| 13.     | Legal information                           | 38 |

| 13.1    | Definitions                                 | 38 |

| 13.2    | Disclaimers                                 | 38 |

| 13.3    | Licenses                                    | 38 |

| 13.4    | Patents                                     | 38 |

| 13.5    | Trademarks                                  | 38 |

| 14.     | Contents                                    | 39 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.

© NXP B.V. 2012.

All rights reserved.

For more information, visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com