# **UM10913**

# PN7462 family Software User Manual

Rev. 1.5 — 14 May 2018 336615

User manual COMPANY PUBLIC

#### **Document information**

| Info     | Content                                                                      |

|----------|------------------------------------------------------------------------------|

| Keywords | PN7462 family FW architecture, ROM FW, flash FW, HAL, examples               |

| Abstract | This document describes the PN7462 family FW architecture and how to use it. |

## **PN7462 family Software User Manual**

## **Revision history**

| Rev | Date     | Description                                                   |

|-----|----------|---------------------------------------------------------------|

| 1.5 | 20180514 | Editorial updates                                             |

| 1.4 | 20180115 | Update for PN7462 family derivates, descriptive title renamed |

| 1.3 | 20172003 | PSP example descriptions revisited                            |

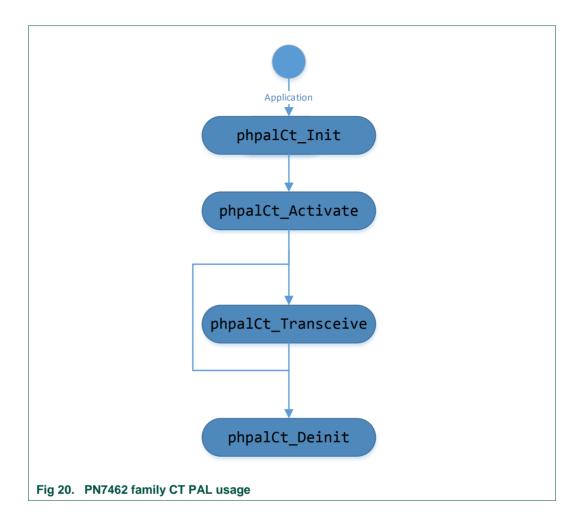

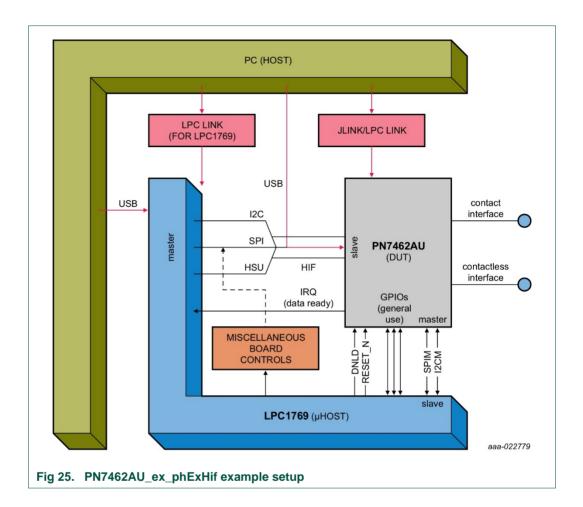

| 1.2 | 20161101 | Fig 20 and Fig 25 updated                                     |

| 1.1 | 20160629 | Section 9 PN7462 family critical sections in HAL added        |

| 1.0 | 20160330 | initial version                                               |

# **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

#### **PN7462 family Software User Manual**

## 1. Introduction

This document describes the PN7462 family FW architecture. The PN7462 family is a family of 32-bit ARM Cortex-M0-based NFC microcontrollers. The PN7462 family consists of six different products: PN7462AUHN, PN7462AUEV, PN7362AUHN PN7362AUEV, PN7360AUHN, PN7360AUEV. They differ from each other in their package, flash size and support for contact smartcard interface.

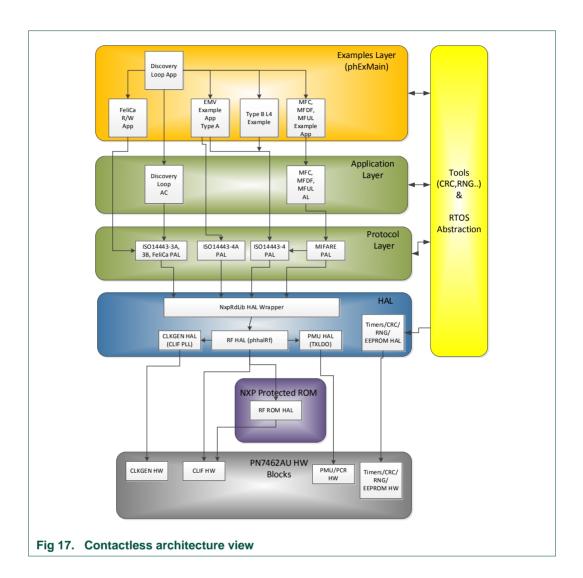

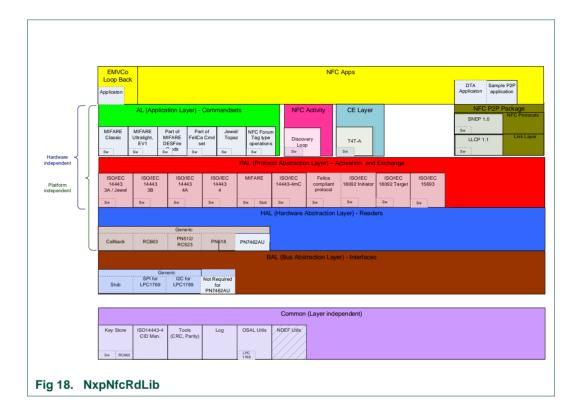

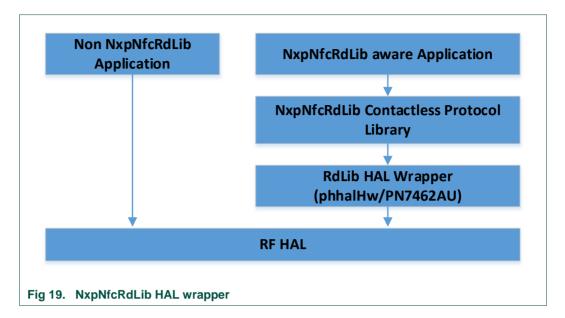

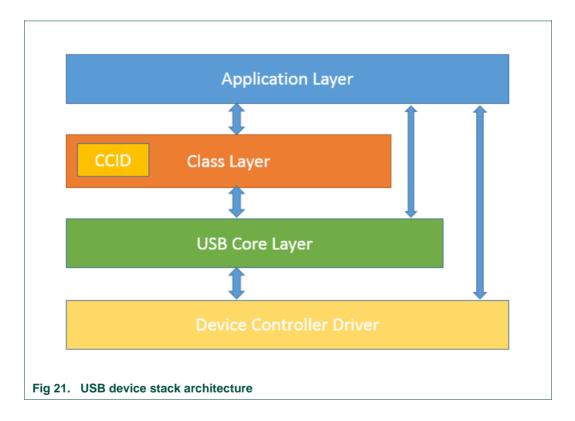

The FW consists of ROM boot, ROM services, flash boot, and hardware abstraction layers. It also includes NXP NFC contactless protocol library, NXP contact library, product support package examples, and RTOS abstraction.

Sections that are not valid for all family members, are marked with a special note.

In this document the terms "MIFARE DESFire card", "MIFARE Classic card" and "MIFARE Ultralight card" refer either to a MIFARE DESFire IC-based contactless card, a MIFARE Classic IC-based contactless card or a MIFARE Ultralight IC-based contactless card.

## 2. PN7462 family FW architecture

## 2.1 PN7462 family FW block diagram

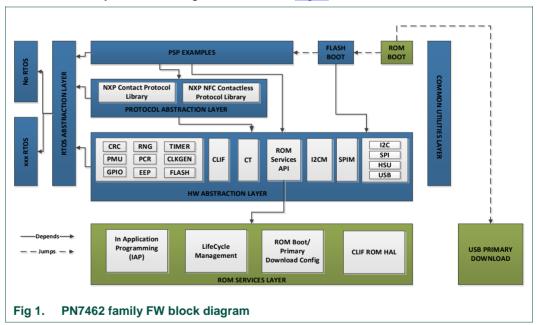

The PN7462 family FW block diagram is shown in Fig 1.

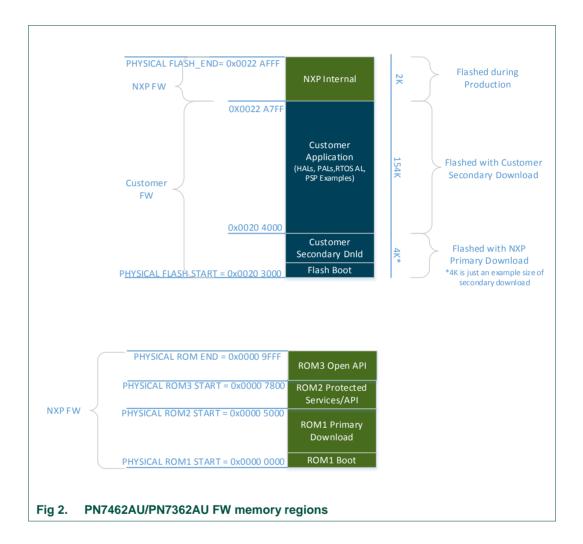

The FW can be divided into NXP FW and user FW. The NXP FW is placed in ROM memory region and protected flash memory region. The user FW is placed in the user flash memory region. The protected flash memory region is primarily used to place ROM patches.

## **PN7462 family Software User Manual**

The NXP FW consists of ROM boot, ROM services and USB primary download. The user FW consists of flash boot, hardware abstraction layers, NXP NFC contactless protocol library, NXP contact library, product support package examples, and RTOS abstraction.

## **PN7462 family Software User Manual**

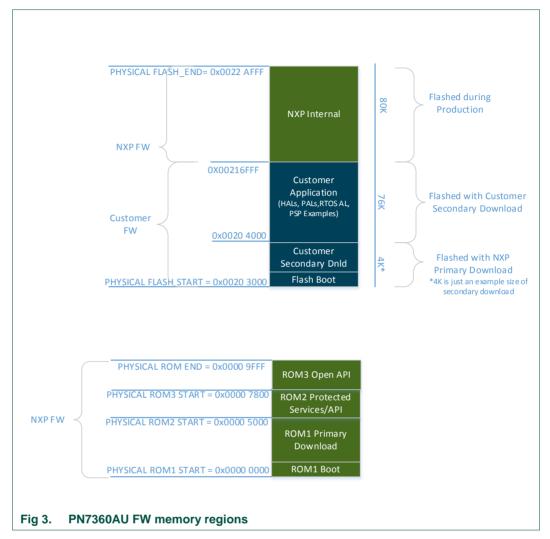

Memory map of the PN7360AU derivative.

In the above diagrams, customer secondary download is shown only as a reference. Secondary download is not explained in this user manual.

## **PN7462 family Software User Manual**

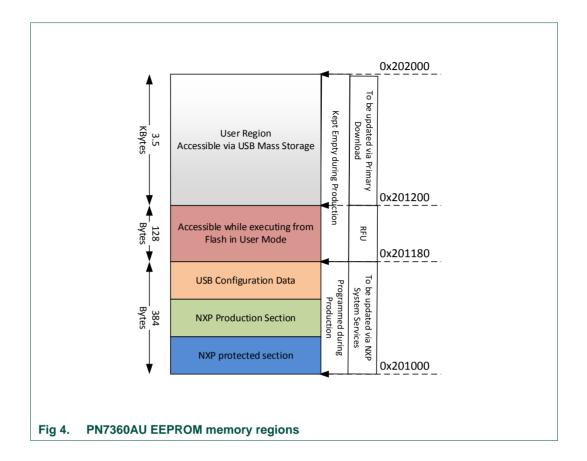

Note: The RFU section of 128 bytes is kept hidden from the aperture of USB mass storage. But this area is used by the HAL executing from the user flash for internal purposes. As of now, there is no special use case for this region and hence in the default examples of PN7462 family, this region remains unused.

## 2.2 PN7462 family FW layer dependencies view

Upon POR or wake-up from IC HPD state or IC standby state, the ROM boot is executed.

For primary download mode, USB primary download code follows the ROM boot.

For user application mode, flash boot follows the ROM boot. The flash boot routine is user accessible whereas the ROM boot routine is **not** user accessible. The flash boot uses HALs for device initialization and executes one of the PSP examples provided in the SW package.

The PSP examples use NXP contact protocol library, NXP NFC contactless protocol library, and HALs to demonstrate user application development. The PSP examples and the HALs use ROM services to execute protected functionality.

## **PN7462 family Software User Manual**

The PSP examples, PALs and the HALs use RTOS abstraction layer to execute. They can execute either with RTOS (such as FreeRTOS) or without RTOS, using single execution context in the thread mode of ARM.

Also, PSP examples, PALs and the HALs use common utilities layer for functions such as memcpy, delay loop, etc. For simplicity, the dependency link is not shown in the diagram.

## 2.3 PN7462 family FW modes

The PN7462 family IC can either be in USB primary download mode or user application mode, depending on the state of DWL\_REQ pin and USB\_VBUS pin at ROM boot execution.

Table 1. PN7462 family FW modes

| DWL_REQ | USB_VBUS | FW mode                   |

|---------|----------|---------------------------|

| 0       | Χ        | user application mode     |

| 1       | 0        | undefined                 |

| 1       | 1        | USB primary download mode |

## 3. PN7462 family ROM FW

## 3.1 PN7462 family ROM boot

The ROM boot is executed upon power-on reset, wake-up from IC hard power-down state and wake-up from IC standby state. The ROM boot performs the following functions:

- 1. Applies the trim values required for proper functioning of the IC.

- 2. Enable the HW blocks that are specified for the product part.

- 3. Start the PVDD LDO in case of internal PVDD configuration.

- Sample the DWL\_REQ pin and USB\_VBUS pin in case pad voltage is available to determine FW mode.

- 5. Perform switch to the modes defined in Table 1.

The ROM boot also switches to user application mode in case no pad voltage is available. For switching to user application mode, the ROM boot performs a vector remapping and a CPU core reset.

The ROM boot communicates the boot result code to flash application through PCR\_GPREGO\_REG register. This result code is apart from HW boot reason which is present in PCR\_BOOT\_REG.BOOT\_REASON and PCR\_BOOT2\_REG.

#### 3.1.1 PN7462 family ROM boot EEPROM config

The PN7462 family ROM boot depends on the EEPROM parameters. These parameters are present in the NXP protected section of EEPROM memory, ranging from 0x201000

## PN7462 family Software User Manual

to 0x20117F. The EEPROM parameters are used by the user according to the system design using ROM Services. The parameters are as follows:

Table 2. ROM boot EEPROM parameters

| Parameter            | Possible value              | Description                                                                                                                                                     | Default value | Max value |

|----------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|

| PVDD source          | internal (0x55)             | if voltage at VBUS pin is > 4 V, ROM boot assumes that PVDD_OUT pin is connected to PVDD_IN pin of the PN7462 familly derivate and starts the internal PVDD LDO | 33 (Auto)     | -         |

|                      | external (0xAA)             | ROM Boot assumes that PVDD_OUT pin is connected to GND and PVDD_IN is connected to external PVDD LDO                                                            | -             | -         |

|                      | auto (others)               | it can be either internal or external HW configuration and the ROM boot detects the configuration                                                               | -             | -         |

| PVDD in time-<br>out | Time-out in units of 100 µs | duration for which the ROM boot waits for external PVDD to arrive or internal PVDD output to stabilize on PVDD_IN pin                                           | 100 ms        | 200 ms    |

| VBUS in time-<br>out | Time-out in units of 100 µs | duration for which the ROM boot waits for VBUS voltage to become greater than 4 V in order to start internal PVDD LDO                                           | 100 ms        | 200 ms    |

## 3.1.2 PN7462 family ROM boot result code

The boot result codes are communicated to flash application through the first 16 bits of PCR\_GPREGO\_REG register. They primarily indicate if PVDD is available and the potential cause, if not available. The boot result codes are as follows:

Table 3. Boot result code

| Boot result code                   | Description                                                                               |

|------------------------------------|-------------------------------------------------------------------------------------------|

| 0x0000, 0x0001, 0x0003             | PVDD is available through internal PVDD LDO                                               |

| 0x0002, 0x0004                     | PVDD is available through external LDO                                                    |

| 0x1000,0x1002,0x1003,0x1007,0x1008 | PVDD is not available at PVDD IN even though internal LDO is turned on                    |

| 0x1001,0x1009                      | VBUS is not greater than 4 V                                                              |

| 0x1004,0x1006                      | PVDD is not available through external LDO                                                |

| 0x1005                             | IC woke up from standby because PVDD disappeared either from internal LDO or external LDO |

## 3.2 PN7462 family ROM primary download

USB primary download is a feature available to the user to download code and data to user flash memory and user EEPROM memory using mass storage application respectively.

Based on the variant size, the user flash memory available in the IC from 0x203000 onwards. For example, for 80 k variants, user flash start: 0x00203000, user flash end:

## **PN7462 family Software User Manual**

0x00216FFF. For 154 k variants, user flash start: 0x00203000, user flash end: 0x002297FF. For 158 k variants, user flash start: 0x00203000, user flash end: 0x0022A7FF

The user EEPROM memory available in the IC is 3.5 K and is situated in the physical address range from 0x201200 to 0x201FFF.

The quick start guide provides information regarding the usage of USB primary download feature.

## 3.2.1 PN7462 family ROM primary download EEPROM config

The PN7462 family ROM primary download depends on the EEPROM parameters. These parameters are present in the NXP protected section of EEPROM memory ranging from 0x201000 to 0x20117F. The EEPROM parameters are used by the user according to their system design using the ROM services. The parameters are as follows:

Table 4. ROM primary download EEPROM parameter

| Parameter                  | Possible value               | Description                                      | Default value | Max value |

|----------------------------|------------------------------|--------------------------------------------------|---------------|-----------|

| code read protection level | 0                            | read, erase and write are allowed                | 0             | -         |

|                            | 1                            | read and erase are not allowed; write is allowed |               |           |

|                            | 2                            | read is not allowed; erase and write are allowed |               |           |

|                            | 3                            | read, erase and write are not Allowed            |               |           |

| data read protection level | 0                            | read, erase and write allowed                    | 0             | -         |

|                            | 1                            | read and erase not allowed; write is allowed     |               |           |

|                            | 2                            | read is not allowed; erase and write are allowed |               |           |

|                            | 3                            | read, erase and write are not allowed            |               |           |

| primary download           | any value other<br>than 0x96 | USB primary download feature is enabled          | 0             | -         |

|                            | 0x96                         | USB primary download feature is disabled         |               |           |

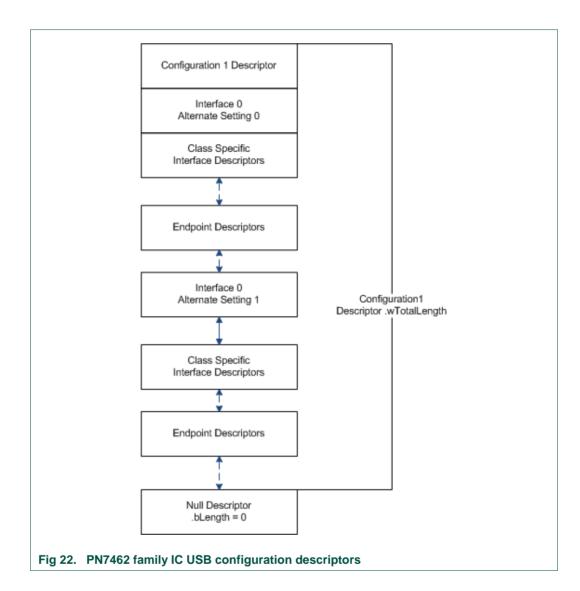

The ROM primary download uses USB interface for enumeration. The configuration required for USB interface can be categorized into two parts:

- 1. USB enumeration-specific configuration.

- 2. USB HW initialization-specific configuration.

The USB enumeration-specific configuration is fairly straightforward. Users may refer to USB specification and ROM services API for more details.

The USB HW initialization-specific configurations are described in <u>Table 5</u>.

## **PN7462 family Software User Manual**

Table 5. Configuration for USB interface

| Parameter                       | Possible value            | Description                                                                          | Default value | Max value |

|---------------------------------|---------------------------|--------------------------------------------------------------------------------------|---------------|-----------|

| USB discharge                   | 0                         | disable fast discharge of USB                                                        | 0             | -         |

|                                 | 1                         | enable fast discharge of USB                                                         |               |           |

| XTAL HW activation time-out     | time-out in units of 1 ms | duration the primary download waits for XTAL oscillator to be up after HW activation | 2 ms          | 255 ms    |

| XTAL SW activation time-out     | time-out in units of 1 ms | duration the primary download waits for XTAL oscillator to be up after SW activation | 2 ms          | 255 ms    |

| USB PLL detection window length | 0-255                     | window length to detect 27.12 MHz PLL input clock                                    | 13            | 255       |

| USB PLL CLK edges               | 0-255                     | number of clock edges to detect 27.12<br>MHz PLL input clock                         | 141           | 255       |

## 3.3 PN7462 family ROM services

The ROM services are accessible via flash APIs present in root\_dir/PN7462AU/phCommon/inc/phhalSysSer.h and with detailed description in API documentation (.chm file). The PN7462 family IC provides ROM services for performing the functions described in sections below.

## 3.3.1 PN7462 family IC lifecycle management services

There are four lifecycle parameters that are used by users at various stages of product development.

#### 3.3.1.1 ROM primary download disable

phhalSysSer\_USB\_PrimaryDnldConfig() is used to irreversibly disable the ROM primary download feature. On subsequent boots, the ROM boot never enters ROM primary download mode, even if DWL REQ pin and USB VBUS pin is high.

This feature is typically used after development and flashing of secondary downloader in the flash memory, for subsequent code/data upgrades.

#### 3.3.1.2 SWD access permissions

When the PN7462 family IC is delivered from production to user, the default SWD access level enables the user to view and debug user flash memory, user EEPROM memory, user RAM memory, and peripheral registers. The access level can be irreversibly changed to prevent view/debug access to any memory region or peripheral registers, before deploying the IC to the field. <code>phhalSysSer\_OTP\_SecrowConfig()</code> can be used to lock the SWD against any further access.

Once SECROW functionality is locked, this feature cannot be used anymore.

## **PN7462 family Software User Manual**

#### 3.3.1.3 Code write protection

It is required to lock flash memory from write at HW level. It is locked possibly at a stage when secure secondary upgrade is **not** planned for the remaining lifecycle of the product. For such use cases, *phhalSysSer\_OTP\_SecrowConfig()* is used to lock flash memory from any further write. Any flash programming after locking the flash results in hard fault.

Once SECROW functionality is locked, this feature cannot be used anymore.

#### 3.3.1.4 RST\_N pin behavior

The SecRow contains the bits that control the behavior of HW related to the RST\_N pin when pad voltage is not available. Two parameters define the RST\_N pin behavior, RST\_N pull-down and RST\_N value.

The *phhalSysSer\_OTP\_SecrowConfig()* is used to control the RST\_N pin behavior.

Table 6. RST\_N pin parameters

| RST_N pull down | RST_N value | HW operation                                                                                                                                    |

|-----------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | X[1]        | pad voltage availability is always assumed in this system; IC checks the status of RST_N pin at POR and enters either HPD or starts ROM booting |

| 1               | 1           | pad voltage availability is not assumed in this system; IC does not check the status of RST_N Signal and starts ROM boot normally upon POR      |

<sup>[1]</sup> X means "any value".

Once SECROW functionality is locked, this feature cannot be used anymore.

#### 3.3.1.5 SecRow lock

The HW SecRow contains the SWD access bits, code write-protection bits and RST\_N pin behavior bits. For blocking any further writes to SECROW register, the phhalSysSer\_OTP\_SetSecrowLock() is used. It prevents further usage of phhalSysSer\_OTP\_SecrowConfig().

Note: phhalSysSer\_OTP\_SecrowConfig() ROM service API should be used considering EEPROM erase/write limitations. If power fails during an EEPROM write, then the state of the location being written is undefined. EEPROM corruption of SECROW register can compromise boot process, since following the POR the bootup sequence is automatically launched to fetch the 32-bit SECROW located in EEPROM protected area. It is recommended to program SECROW register at the production time only once.

## **PN7462 family Software User Manual**

## 3.3.2 PN7462 family ROM boot configuration

phhalSysSer\_USB\_PVDD\_Config() is used to configure the ROM boot EEPROM configuration; see Section 3.1.1.

## 3.3.3 PN7462 family ROM primary download configuration

phhalSysSer\_USB\_PrimaryDnldConfig() and phhalSysSer\_USB\_Config() is used to configure the ROM primary download EEPROM configuration; see Section 3.2.1.

## 3.3.4 PN7462 family in-application programming

phhalSysSer\_SetFlashProgram() is used during secondary FW upgrade developed by the user. Since the secondary downloader of the user executes in flash memory, it cannot write (programmed) at the same time. Hence the programming of flash page is performed from ROM memory and hence this API.

This API returns an error if code write protection is enabled in SECROW register.

## 3.3.5 PN7462 family CLIF ROM HAL

The CLIF ROM services contain a number of HAL functions. These functions are internally used by the CLIF flash HAL and are not supposed to be directly used by the user application code. Hence, these services are not described in this user manual.

#### 3.3.6 Utilities

The ROM Services provide 2 utilities to customer.

#### 3.3.6.1 CPU reset from flash boot

PN7462 family IC reset always results in ROM booting. However, if the booting has to be done directly from the flash (for example, perform ARM core reset only), the API *phhalSysSer\_SetCPU\_Reset()* is used. The digital peripherals are **not** reset and may contain residual state.

#### 3.3.6.2 Get die ID

It is a unique IC-specific ID stored in the NXP protected section of EEPROM. User can use *phhalSysSer\_GetDieID()* to read this value and further use for their security algorithms (for example, key diversification).

**PN7462 family Software User Manual**

# 4. PN7462 family user FW

# 4.1 PN7462 family flash boot

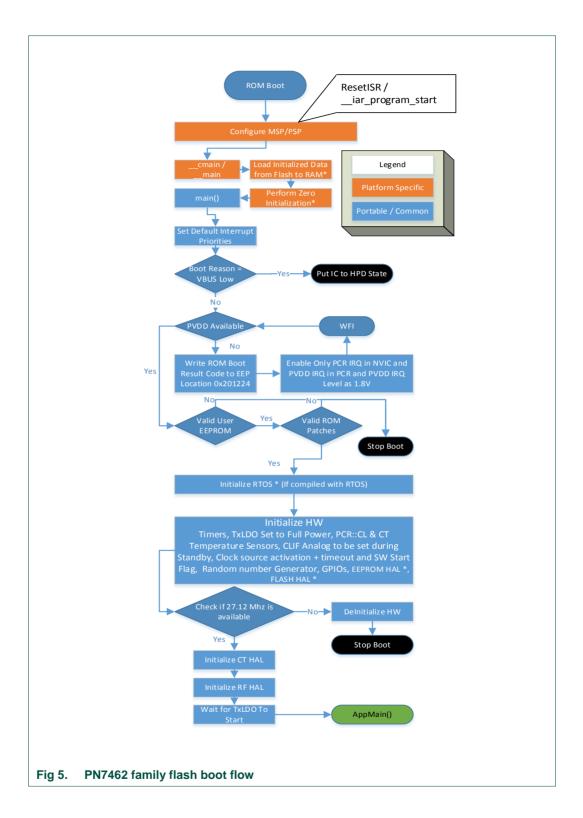

The flash boot is executed when ROM boot performs a vector remapping and the CPU is reset. The relevant functions are present in /root dir/PN7462AU/phBoot/src.

The functions performed by flash boot (before jumping to one of the PSP examples) and the sequence of flow is shown in  $\underline{\text{Fig 5}}$ . The total time taken for flash boot in NXP provided reference package is ~900  $\mu$ s.

At the end of flash boot, execution always calls AppMain().

## **PN7462 family Software User Manual**

#### **PN7462 family Software User Manual**

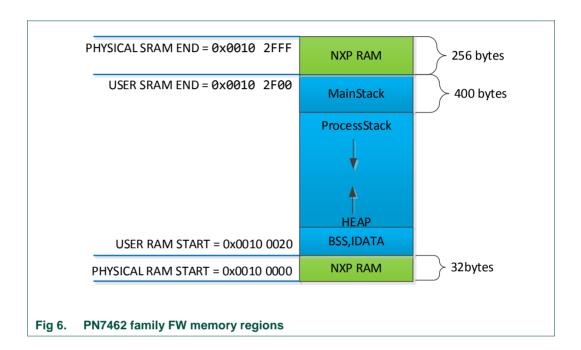

## 4.1.1 ARM CPU and RAM regions initialization

The ARM is configured to execute from thread mode. The Main Stack Pointer (MSP) is initialized to the top of user SRAM. The user SRAM region is between 0x102000 to 0x102BFF. The process stack pointer is initialized after end of MSP. The process stack and the heap grow towards each other. The user has to ensure that the process stack and heap do not corrupt each other. The PSP/MSP initialization is done in "phFlashBoot\_GCC.c" in MCUXpresso project and in "phFlashBoot\_IAR.s" in iAR project. In the Keil project, the "startup\_PN74xxxx.s" (part of Keil MDK PN7xxxx installer pack) initializes the PSP/MSP. The user SRAM is limited to 12000 bytes and 256 bytes is used by NXP FW executed in ROM.

## 4.1.2 BSS and IDATA initialization

Due to real-time target mode requirements (response within 5 ms of ROM boot), the flash boot time shall be as low as possible. Hence, the FW shall not contain any IDATA and shall also work with BSS **not** initialized to zero.

At 20 MHz, it takes approximately 171 us to zero initialize 976 bytes of data. This value represents combined ZI data for the Application + Protocol Library + RTOS + HALs. Its size varies based on the application and the configuration of the application (Used HALs, RTOS, Protocols, etc.) itself.

Ideally, the FW may potentially work even with BSS non-initialized to zero. But with integration of many commercially available RTOS or protocol libraries such as NxpNfcReaderLibrary, there is bound to be few bytes of initialized data and a requirement to initialize BSS with zero. Hence to keep the zero initialization to a minimum, *PH NOINIT* is used to exclude variables from zero-init.

## **PN7462 family Software User Manual**

## 4.1.3 Default interrupt priorities

The interrupt priorities are application-dependent. Hence, there are few restrictions on the user with regards to interrupt priority setting. SVC is used for application purposes. However, ROM services shall **not** be called from SVC handler since ROM uses SVC handler for patch mechanism. Similarly, SVC handler must be set to highest priority before calling system services. The typical interrupt priority settings are shown below and are set in *phFlashBoot\_SetIntrptsPrio()*.

Table 7. Default interrupt priorities

| Exception/IRQ                              | Priority                    | Description                                                                                                                |

|--------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|

| RESET                                      | -3 (highest)                | reset ISR                                                                                                                  |

| NMI                                        | -2                          | upon watchdog timer expiry                                                                                                 |

| HardFault                                  | -1                          | upon invalid memory accesses                                                                                               |

| SVC                                        | PH_HAL_INTRPT_PRIO_REALTIME | used by system services function; is used by user application, but system services shall not be called from an SVC handler |

| CLIF, HIF, CTIF,<br>PMU, PCR               | PH_HAL_INTRPT_PRIO_HIGH     | interfaces ISR and system event ISRs                                                                                       |

| Timer, EECNTRL,<br>SPIM, I <sup>2</sup> CM | PH_HAL_INTRPT_PRIO_HIGH     | utility ISRs and master interfaces                                                                                         |

| PendSV, SysTick                            | PH_HAL_INTRPT_PRIO_LOW      | context switching ISRs                                                                                                     |

## 4.1.4 Boot reason and result code handling

The flash boot checks PCR registers for exceptions in the boot reason and boot result code provided by the HW and ROM boot respectively; see <u>Section 3.1.2</u>.

If the HW boot reason is VBUS\_LOW, it means that the IC wakes up from standby because the VBUS dropped below threshold. In such cases, the flash boot configures the IC to enter hard power down state. If there is any other boot reason, the flash boot checks for pad voltage availability. If the pad voltage is not available, it writes the boot result code to EEPROM location 0x201224 and waits for PVDD to arrive, by executing WFI (ARM SLEEP instruction).

The exception checks are performed using phFlashBoot\_PreCheck().

## 4.2 PN7462 family HALs initialization at boot UP

The following initialization happens during default boot up of PN7462 family derivate.

## 4.2.1 Temperature sensor initialization and RF standby configuration

The PN7462 family products contains two temperature sensors, one for contactless front end and another for contact front end (for some products the contact interface is not

## PN7462 family Software User Manual

available). In this initialization, the temperature sensors are enabled and the lower and upper thresholds are configured.

The CLIF transmitter analog configuration required during standby/suspend are also initialized.

During USB suspend, a set of registers are configured to reduce the power configuration. This set of registers are provided during initialization.

It is recommended not to change the value different from the default value in EEPROM.

Table 8. EEPROM parameters for temperature sensors - PcrPwrTempConfig

Power clock reset temperature configuration related to phhalPcr PwrTempConfig t

| Туре | Field name                | Default value | Description                                         |

|------|---------------------------|---------------|-----------------------------------------------------|

|      |                           |               | flag to indicate to use temperature sensor 0 or not |

| u8   | bUseTempSensor0           | 0             | 0: Disabled                                         |

|      |                           |               | 1: Enabled                                          |

|      |                           |               | flag to indicate to use temperature sensor 1 or not |

| u8   | bUseTempSensor1           | 0             | 0: Disabled                                         |

|      |                           |               | 1: Enabled                                          |

|      |                           |               | 0 : 135                                             |

| u8   | bLowTempTarget0           | 3             | 1:130                                               |

| uo   | beow rempraigeto          | 3             | 2:125                                               |

|      |                           |               | 3:120                                               |

|      |                           |               | 0:135                                               |

| u8   | bLowTempTarget1           | 3             | 1:130                                               |

| uo   | DLowrempraigeri           | 3             | 2:125                                               |

|      |                           |               | 3:120                                               |

|      |                           |               | 0 : 135                                             |

| u8   | bHighTempTarget0          | 0             | 1:130                                               |

| uo   | bi ligit i ettip i argeto | U             | 2:125                                               |

|      |                           |               | 3:120                                               |

|      |                           |               | 0 : 135                                             |

| u8   | bHighTempTarget1          | 0             | 1:130                                               |

|      |                           |               | 2:125                                               |

For a detailed parameter description, and parameter addresses in the EEPROM refer to the EEPROM description [2] file.

Table 9. EEPROM parameters for power down settings - PcrPwrDown

It is a 32-bit value bit-file created by ORing enums of type phhalPcr\_PwrDown\_Setting\_t used to select which settings must be applied to reduce power consumption during suspend.

| Туре | Field name        | Default value | Description                                                                                   |

|------|-------------------|---------------|-----------------------------------------------------------------------------------------------|

| u32  | dwPwrDownSettings | 0x7FFFFFF     | 0x7FFFFFFF: E_APPLY_ALL_SETTNGS. i.e. all power reduction settings are applied during suspend |

#### **PN7462 family Software User Manual**

Table 10. EEPROM parameters for temperature sensors - TxAnaStandByConfing

TxAna register settings for standby; See phhalPcr\_TxAnaStandByConfig\_t

| Туре | Field name                     | Default value | Description                                          |

|------|--------------------------------|---------------|------------------------------------------------------|

| u32  | dwAna Tx StandBy<br>Value      | 0x0F          | to hold CLIF standby GSN value selection             |

| u32  | dwAna Tx Pro tStandBy<br>Value | 0x03          | to hold the CLIF configuration related to power-down |

For a detailed parameter description and parameter addresses in the EEPROM refer to the EEPROM description [2] file.

#### 4.2.2 CLKGEN initialization

The CLKGEN HW can have two sources: XTAL or external clock. Depending on the crystal characteristics, the activation time-out can be different. If HW activation fails, the HAL and HW provides a mechanism to perform SW activation. All these options are initialized during the flash boot.

The user shall modify the EEPROM according to the board/system design.

Table 11. EEPROM parameters for CLKGEN - Clkgen

Clock generator. See phhalClkGen Init

| Туре | Field name                 | Default value | Description                                              |

|------|----------------------------|---------------|----------------------------------------------------------|

| u16  | w Xtal Activation Time Out | 2000          | dwXtalActivationTimeOut activation time-out value        |

| u8   | eSource                    | 0x00          | eSource clock source selection, See phhalClkGen_Source_t |

| u8   | bKickOnError               | 0x00          | bKickOnError kick on error.                              |

For a detailed parameter description and parameter addresses in the EEPROM, refer to the EEPROM description [2] file.

#### 4.2.3 CLIF transmitter TxLDO initialization

The TxLDO used for CLIF transmitter is initialized as part of the boot. The parameters such as whether internal TxLDO is used or external TxLDO is used, the power configuration for full power (used in reader mode and SL-ALM card mode if internal TxLDO is used), low power configuration (for PLM card mode), TxLDO start-up time and over current enable are configured.

The user shall modify the EEPROM according to the board/system design.

## PN7462 family Software User Manual

Table 12. EEPROM parameters for PMU – CLIF transmitter TxLDO

Power management unit. (See phhalPmu TxLdoInit and phhalPmu TxLdoParams t)

| Type | Field name         | Default value | Description                                                                                                 |  |

|------|--------------------|---------------|-------------------------------------------------------------------------------------------------------------|--|

| u8   | bUseTxLdo          | 0x01          | parameter to use internal TxLDO or to use external TxLDO 0: do not use internal TxLDO 1: use internal TxLDO |  |

|      |                    |               | TVDD Sel for reader mode. See phhalPmu_TvddSel_t                                                            |  |

|      |                    |               | 0: 3 V                                                                                                      |  |

|      |                    |               | 1: 3.3 V                                                                                                    |  |

| u8   | eFullPowerTvddSel  | 0x04          | 2: 3.6 V                                                                                                    |  |

|      |                    |               | 3: 4.5 V                                                                                                    |  |

|      |                    |               | 4: 4.7 V                                                                                                    |  |

|      |                    |               | other: invalid                                                                                              |  |

|      |                    |               | Source for the TVDD See phhalPmu_LowPower_TvddSrc_t                                                         |  |

|      |                    |               | 0: source is TVDD In                                                                                        |  |

| u8   | eLowPowerTvddSrc   | 0x01          | 1: source is VUP                                                                                            |  |

|      |                    |               | 2: source is VBUS                                                                                           |  |

|      |                    |               | other: invalid                                                                                              |  |

|      |                    |               | Over current interrupt                                                                                      |  |

| u8   | bOverCurrentEnable | 0x00          | 0: Disabled                                                                                                 |  |

|      |                    |               | others: Enable                                                                                              |  |

| u16  | wWaitTime          | 250           | waiting time after the TxLDO is started 250us is typical value.  Maximum 500us                              |  |

For a detailed parameter description and parameter addresses in the EEPROM, refer to the EEPROM description [2] file.

## 4.2.4 RNG HW Initialization

The time-out for true random number generation is initialized. It is recommended not to change the value different from the default value in EEPROM.

Table 13. EEPROM parameters for RNG HW - RNG

Random Number Generator. See phhalRng\_Init

| Туре | Field name                 | Default value | Description                                       |

|------|----------------------------|---------------|---------------------------------------------------|

| u16  | w Xtal Activation Time Out | 2000          | dwXtalActivationTimeOut activation time-out value |

For a detailed parameter description and parameter addresses in the EEPROM, refer to the EEPROM description [2] file.

#### 4.2.5 GPIO initialization

The GPIOs are initialized for I/O and pullup/pulldown in case of input and slew rate in case of output.

The customer shall modify the EEPROM from where the GPIO initialization configuration is taken in accordance to the board/system design.

**PN7462 family Software User Manual**

Table 14. EEPROM parameters for GPIO

GPIO Bootup configuration. Each byte represents a GPIO configuration starting from GPIO 1 to 12. See phCfg\_EE\_Boot\_GPIO\_t.

| Туре   | Field name | Default value                                      | Description                                                                                                                                                                                                                                                        |

|--------|------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |            |                                                    | lower nibble - related to output configuration upper nibble - related to pull-up/pull-down configuration                                                                                                                                                           |

| u8[12] | OutputPUPD | 00 00 00 00<br>00 00 03 03<br>07 03 03 03<br>(hex) | Bit0 = 0: skip configuration as output on boot Bit0 = 1: configure GPIO as output Bit1 = 1: enable slew-rate Bit2 = 1: drive the output high Bit2 = 0: drive the output low Bit5 = 1: apply pull-up Bit6 = 1: apply pull-down                                      |

| u8[12] | InputISR   | 00 00 00 00<br>00 00 00 00<br>00 00 00 00<br>(hex) | ALL = 0: skip configuration on boot Bit0 = 0: unconfigure as input Bit0 = 1: configure/SET as input Bit1 = 1: GPIO is a wake-up source Bit2 = 1: GPIO is an interrupt source Bit4 = 1: level sensitive interrupt Bit5 = 1: interrupt on active low or falling edge |

For a detailed parameter description and parameter addresses in the EEPROM refer to the EEPROM description [2] file.

## 4.2.6 General-purpose timers initialization

The PN7462 family product contains four general-purpose timers. The HAL context to manage the timer requests are initialized during the flash boot.

#### 4.2.7 Clock 27.12 MHz check

In PN7462 family product, the FW always assumes the availability of 27.12 MHz clock sourced from either external crystal or external clock. This clock is required for all communication interfaces and flash programming. If a crystal is used, PN7462 family HW has a crystal oscillator that is activated by default and it takes maximum of 2 ms to activate and generate stable 27.12 MHz clock.

For this purpose, the flash boot performs most HW initialization to utilize the XTAL activation time. Hence the flash boot checks if the 27.12 MHz is available and if not available de-configures all HALs and stops booting. If available, flash boot proceeds to initialization of HALs that require 27.12 MHz clock.

## **PN7462 family Software User Manual**

#### 4.2.8 EEPROM/flash HAL initialization

These HALs are not used in a typical contactless or contact application. They are used during secondary downloader application. By default, these HALs are disabled. The compile-time directives, *NXPBUILD\_PHHAL\_EEPROM* and *NXPBUILD\_PHHAL\_FLASH* enable the HALs.

After the common HALs initialization, the flash boot jumps to user application program.

Note: The secondary bootloader is placed directly after the flash boot code and provides the functionality to download a user application program; see Fig 2. The HAL API provides functions that enable to read and write user data on the flash or EEPROM. All the functions are described in PN7462AU FW API Guide document under "Hardware Abstraction Layer - Generic HALs - FLASH HAL / EEPROM HAL" and in the files "root\_dir/PN7462AU/phCommon/inc/ phhalFlash.h" and "root\_dir/PN7462AU/phCommon/inc/phhalEeprom.h". Use NXPBUILD\_\_PHHAL\_EEPROM and NXPBUILD\_\_PHHAL\_FLASH compile-time directives to enable them. By default, both directives are disabled and are available in "ph\_NxpBuild\_Default.h".

During data reading and writing, best time is achieved with flash HIGH perf ON and ramp clock ON.

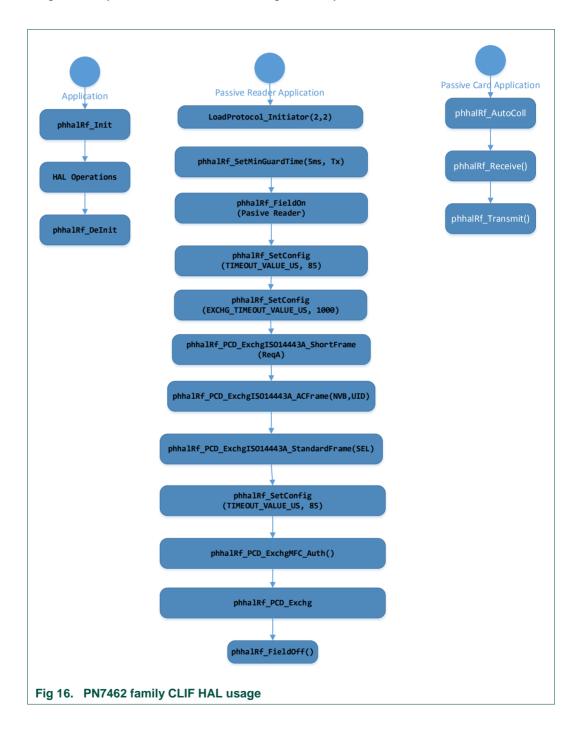

#### 4.2.9 RF HAL initialization

The CLIF IP registers are set to pre-defined values from EEPROM and few registers are reset to default values. Event mechanisms are initialized to act as IPC between ISR and HAL. This initialization prepares the RF HAL to transition to either target mode if external RF field is present or reader mode if application wishes.

By default, the operating mode of CLIF HAL is set to NFC Forum mode. It means that the guard times for various technologies are applied according to NFC Forum. All spurious interrupts are cleared and interrupt enabled at ARM level (NVIC interrupt).

Also, the DPC feature for reader mode and APC feature for SL-ALM card mode are initialized.

The EEPROM required for CLIF is split into 2 memory regions: One common region and one protocol-specific region.

#### 4.2.10 CT HAL initialization

The CLIF IP registers are set to pre-defined values from EEPROM and few registers are reset to default values. Event mechanisms are initialized to act as IPC between ISR and HAL. Primarily the connector type (open/closed), pull-up/pull-down configuration, automatic CT deactivation and slew rate of the contact pads are configured.

If the pull-up/pull-down configuration is mismatched between the EEPROM and the actual setting on board, spurious interrupt may occur.

The customer shall modify the EEPROM in accordance to board/system design.

## **PN7462 family Software User Manual**

Table 15. EEPROM parameters for CT

Initial settings for CT interface. See also phhalCt\_InitParam\_t

| Type | Field name                      | Default value | Description                                                                                                               |

|------|---------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------|

| u8   | bPullUp                         | 1             | pull up configuration  0: pull-down                                                                                       |

| 40   | S. dilep                        | ·             | 1: pull-up others: undefined behavior                                                                                     |

| u8   | bConnectorType                  | 1             | connector type 0: normally closed others: normally open                                                                   |

| u8   | bAuto CT Deactivation<br>Enable | 1             | auto deactivation 0: Disabled others: Enabled                                                                             |

| u8   | bSlewRate                       | 0x38          | CLK,IO,VCC slew rate  0: CLK,IO,VCC slew rate  others: This value is directly mapped to ct_srr_reg to give enough options |

For a detailed parameter description and parameter addresses in the EEPROM, refer to the EEPROM description [2] file.

Note: Not all PN7462 family products have the CT interface

#### 4.2.11 HAL deinitialization

If any of the initializations fail, all the HALs are de-initialized in the phFlashBoot HwTearDown() API.

## 4.3 PN7462 family generic HALs

For details of HAL functions and their description, refer to the API guide (CHM document). In the sections discussed below, functional usage of the HALs are described. The usage activity diagrams show a representation of usage and parameters.

To provide more memory for customer application, some of the below HAL functions are completely or partially moved to ROM3 region. The "PN7462AU\_ROM3.h" contains the ROM3 functions that are used internally by the flash HAL implementation or flash HAL API.

## **PN7462 family Software User Manual**

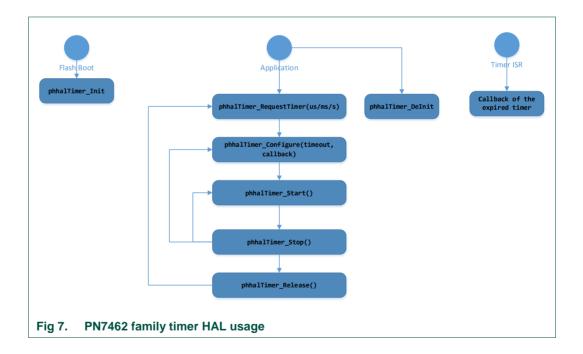

#### 4.3.1 Timer HAL

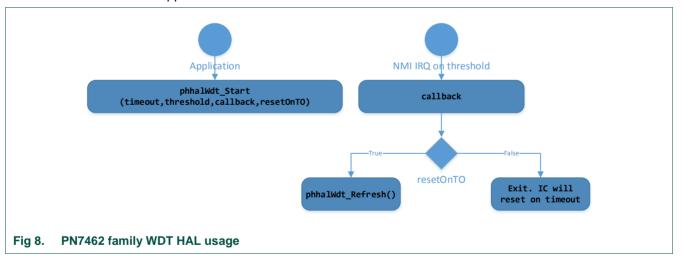

The PN7462 family IC provides four general-purpose timers, watchdog timer and system tick timer.

The SysTick timer is used for RTOS scheduler and is initialized in the RTOS-specific configuration file.

The general-purpose timer 0 and timer 1 are 12-bit timers at 3 kHz frequency. Timer 2 and Timer 3 are 32-bit timers at 20 MHz frequency. The Timer 0 and Timer 1 can be concatenated as a single timer with Timer 1 incrementing a step upon Timer 0 completion.

The Timer HAL provides APIs to manage the lifecycle of an HW timer; see Fig 7.

Upon request of a timer for a time unit (microsecond/millisecond/second), the timer HAL allocates the HW timer according to <u>Table 16</u>.

Upon successful timer request, the allocated timer may be configured for different timeouts and callbacks after one or multiple start-stop cycles.

The timer IRQ executes the callback in the ISR context.

The flash HAL implementation provides a wrapper for context management and the core register functions are present in ROM3.

## PN7462 family Software User Manual

Table 16. HAL timer allocation

| Timer             | Width  | Frequen<br>cy | Min to  | Max to                  | Recommended use                                                        |

|-------------------|--------|---------------|---------|-------------------------|------------------------------------------------------------------------|

| Timer 0           | 12-bit | 3 kHz         | 330 µs  | 1351 ms                 | millisecond timer                                                      |

| Timer 1           | 12-bit | 3 kHz         | 330 µs  | 1351 ms                 | millisecond timer                                                      |

| Timer 0 & Timer 1 |        | 3 kHz         |         | 4095 × 1351 ms = 5532 s | first priority: seconds timer<br>second priority: millisecond<br>timer |

| Timer 2           | 32-bit | 20 MHz        | 50 ns   | 215 s                   | first priority: microsecond                                            |

| Timer 3           | 32-bit | 20 MHz        | 50 ns   | 215 s                   | timer<br>second priority: seconds timer                                |

| Watchdog          | 10-bit | 45 Hz         | 21.5 ms | 22 s                    | recovery from HW or SW hangs or loops                                  |

The watchdog timer is a 10-bit timer at an approximate frequency of 45 Hz. Upon watchdog timer expiry, the watchdog timer asserts an IC reset. In order to perform recovery or cleanup tasks, a watchdog threshold is available. Upon watchdog threshold, FW is interrupted with an NMI and the FW can choose to re-initialize the watchdog timer or perform cleanup (before IC is reset). The activity flow is shown in Fig 8.

The WDT HAL is implemented in flash HAL since customer may modify it according to the application.

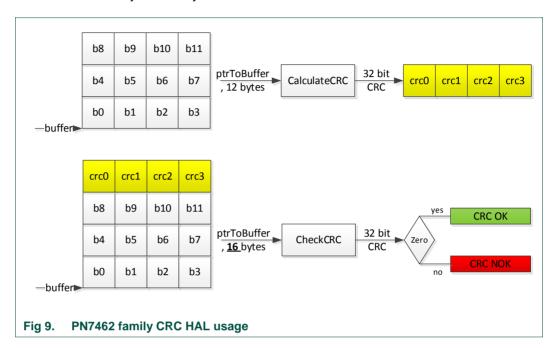

## 4.3.2 CRC HAL

The PN7462 family IC provides a CRC co-processor to compute 16/32-bit CRC for a 32/16/8-bit input data. The co-processor computes the 16/32-bit CRC in parallel, providing the output in one clock cycle. The CRC computation can be done with MSB first or LSB first of input data stream. The CRC HAL provides the following functions:

• Calculate the CRC over a buffer of arbitrary length.

## **PN7462 family Software User Manual**

• Check the CRC of a buffer of arbitrary length with supplied CRC. The supplied CRC shall be last 2 bytes or 4 bytes of the buffer.

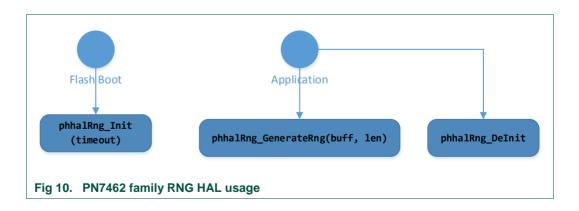

#### **4.3.3 RNG HAL**

The PN7462 family IC provides an RNG co-processor that generates pseudo-random numbers. The RNG HAL provides APIs to generate one or more random numbers. The *phhalRng\_GenerateRng* returns time-out error if random number is **not** generated within the initialized time-out.

This HAL is implemented in ROM3.

## **PN7462 family Software User Manual**

## 4.4 PN7462 family master interface HALs

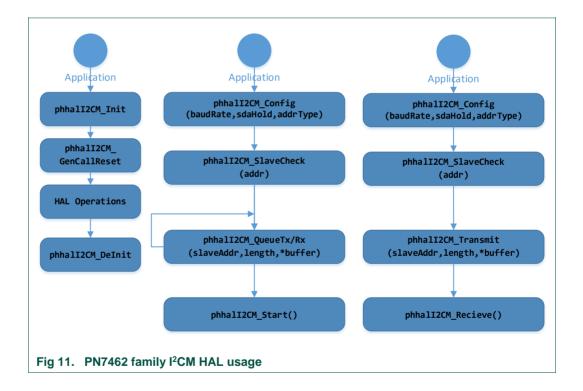

#### 4.4.1 I2CM HAL

The I<sup>2</sup>CM HAL provides the following features.

## 4.4.1.1 Device-specific configuration

- 1. TX/RX FIFO threshold.

- 2. TX/RX completion time-out since the HALs are blocking.

- 3. Retry count of any transaction.

- The phhalll2CM\_Init() and phhall2CM\_DeInit() used to set/reset this configuration.

## 4.4.1.2 Slave specific configuration

- Baud rate

- The SDA hold time

- 7-bit or 10-bit Address type of the slave

The baud rate is used to calculate the SCL frequency based in the equation. Users shall calculate the baud rate field according to their required SCL frequency

$$SCL_{Frequency} = \frac{27.12 \, MHz}{(27 + Boudrate)}$$

• The phhall2CM\_Config() is used for configuration.

#### 4.4.1.3 Slave presence check

The phhall2CM SlaveCheck() is used to perform this check.

#### 4.4.1.4 I2C-bus reset

- General call reset addressing is used to reset the I<sup>2</sup>C-bus that resets all attached slaves.

- The *phhall2CM\_GenCallReset()* is used to for configuration.

#### 4.4.1.5 Single transaction

- This feature is used when the length of the transaction is greater than 32 bytes.

- The *phhall2CM\_Transmit()* and *phhall2CM\_Recieve()* are used to perform this transaction.

#### 4.4.1.6 Multiple transactions

• This feature is used when multiple short (less than 4 bytes, 8 bytes, or 16 bytes) transactions are done to a single slave such as TDA registers read or write

## **PN7462 family Software User Manual**

- The phhall2CM\_QueueTx(), phhall2CM\_QueueRx() and phhall2CM\_Start() are used to perform these transactions.

- These features are by compile time macro NXPBUILD PHHAL I2CM MULTI TRANSACTION

#### 4.4.1.7 Device reset

- This feature is used to reset the I<sup>2</sup>CM HW in cases when the bus is idle due to HW stuck in an erroneous bus condition. This is **not** I<sup>2</sup>C bus reset explained in item (4)

- The phhall2CM\_Reset() is used to perform this feature.

#### 4.4.1.8 I<sup>2</sup>CM HAL usage overview

The I<sup>2</sup>CM Core register functions are implemented in ROM3 and logical functions are implemented in flash HAL.

## **PN7462 family Software User Manual**

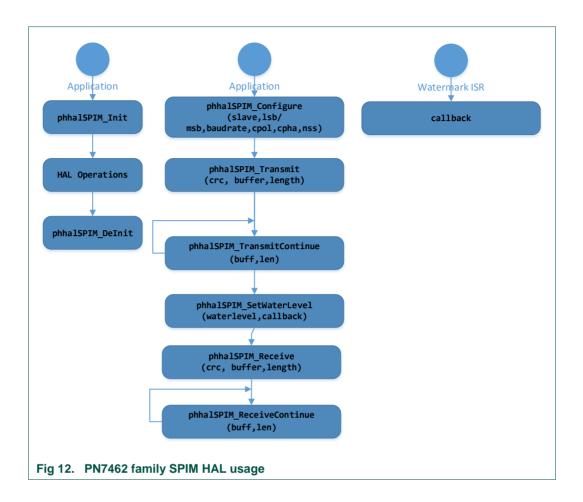

#### **4.4.2 SPIM HAL**

The SPIM HAL provides the following features.

#### 4.4.2.1 Device-specific configuration

- TX/RX completion time-out since the HALs are blocking.

- phhalSPIM Init() and phhalSPIM Delnit() are used to set or reset this configuration.

#### 4.4.2.2 Slave specific configuration

- · Slave to be configured

- · MSB or LSB first transmission

- CPOL/CPHA modes

- · Baud rate

- NSS-specific configuration

- phhalSPIM\_Configure() used to perform this configuration

#### 4.4.2.3 TX/RX transactions

Since SPIM can be used for SD card use case, CRC configuration is required for some transactions and **not** required for some transactions to the same slave. Hence, every transaction has CRC configuration which can be enabled or disabled. phhalSPIM\_Transmit() / Receive() / Transmit\_Continue() / Receive\_Continue() are used for transactions.

#### 4.4.2.4 Water level configuration

Since SPIM HW is DMA-based, water level interrupt can be used to detect early reception complete or transmission complete and synchronize dependent functions. phhalSPIM\_SetWaterLevel() is used to set the water level and the function callback is called in case there is a water level interrupt.

The SPIM Core register functions are implemented in ROM3 and logical functions are implemented in flash HAL.

## **PN7462 family Software User Manual**

#### 4.5 Host interface HAL

The PN7462 family provides four host interfaces to communicate with a host processor. The sections described below explain the functions of the host interface. At any instance, only one host interface shall be used. Within a boot session of PN7462 family product, only one host interface is assumed and dynamic switching between host interfaces without an intermediate reset is **not** assumed.

The host interface can be I<sup>2</sup>C, SPI, HSU or USB.

## 4.5.1 I<sup>2</sup>C

The HIF HAL initializes the I<sup>2</sup>C physical interface with 7-bit slave address and enables or disables HW response to device ID request from external I<sup>2</sup>CM. It also configures whether I<sup>2</sup>C core should reset the complete IC when receiving general call address for I<sup>2</sup>C-bus reset. It also configures if the I<sup>2</sup>C slave should switch to HS mode upon request from I<sup>2</sup>CM master.

## PN7462 family Software User Manual

#### 4.5.2 SPI

The HIF HAL initializes the SPI physical interface with either of the four modes of SPI operation.

Table 17. SPI operation modes

| CPOL        | СРНА                 |

|-------------|----------------------|

| Active low  | sampling @ even edge |

| Active low  | sampling @ odd edge  |

| Active high | sampling @ even edge |

| Active high | sampling @ odd edge  |

#### 4.5.3 HSU

The HIF HAL initializes the HSU physical interface with the EOF size, baud rate and number of stop bits. The interface can also be initialized with auto baud rate estimator. If the baud rate estimator is enabled, the HIF HAL ensures that no transmission can take place without first reception.

#### 4.5.3.1 HSU standby scenario

When a host sends some frames over HSU during the time PN7462 family IC is in standby, one to three bytes of frame are lost. They are characterized and the host shall always send dummy one to three bytes before actual frame. To make buffer management simple, HIF HAL always reserves the dummy bytes in the buffer. It is done so that the received frame is stored at the same offset every time.

The host interface HAL provides initialization API to configure above HW features – *phhalHif\_Init()* API.

#### 4.5.4 USB

The USB device controller enables USB 2.0 full-speed (12 Mbit per second) data exchange with a USB host controller and USB 3.0 hub connection capability.

#### 4.5.5 Frame interfaces

The PN7462 family HIF provides three different frame interfaces as described below. The frame interface to be chosen is initialized using *phhalHif\_Init()* API.

#### 4.5.5.1 Fixed-format frame interface

In this frame interface, the host processor (e.g.: LPC) and the HIF HW of PN7462 family IC agrees that the frames to be exchanged shall have a header containing the length and a trailer containing the 16-bit CRC. The header shall be minimum 2 bytes and maximum of 4 bytes. The length field can be maximum of 10 bits and can be positioned anywhere within the header.

When the HIF HAL is configured for fixed-format frame interface,

## **PN7462 family Software User Manual**

- At reception, the HW shall retrieve the length from the first 2/3/4 bytes of received data (e.g.: header) and shall count that many bytes of payload of further reception.

After the payload, the HW checks the CRC of the received payload.

- Similarly, at transmission, the HW shall retrieve length from the first 2/3/4 bytes of transmit buffer and shall transmit the bytes as payload from the transmit buffer. After that, the HW appends the 16-bit CRC.

Maximum payload that can be transmitted or received is 1024 bytes.

#### 4.5.5.2 Free format frame interface

In this frame interface, the host processor and the HIF HW of PN7462 family IC do not agree on any fixed format of the frame. Hence the HIF HW cannot parse the header and know the length of payload. Hence, the HIF HW cannot count the number of transmitted or received bytes and also cannot perform CRC checking or generation. Hence,

- At reception, the HIF HW uses the physical interface start and stop conditions to determine the length of reception.

- At transmission, a TX length register to determine the length of transmission.

The HIF application has to perform CRC checking/generation. The format that is configured is applicable to both TX and RX.

Maximum payload that can be transmitted or received is 250 bytes.

#### 4.5.5.3 Native format frame interface

This format is same as free format with the exception that the maximum payload that can be transmitted or received is 1024 bytes.

#### 4.5.6 Buffer interface HAL

The HIF HW in PN7462 family IC provides four RX buffers and one TX buffer. The HIF HAL provides APIs for HIF application to request RX buffer and release RX buffer. The HAL also provides APIs to send TX buffer. The access to these APIs is allowed in single task context only. The HAL manages the error handling in case of fixed-format mode. The HAL configures the HW to either discard erroneous buffer or retain the buffer and pass it to the application.

The ISR calls the callback function upon reception complete or transmission complete.

The HIF Core register functions are implemented in ROM3 and logical functions are implemented in flash HAL.

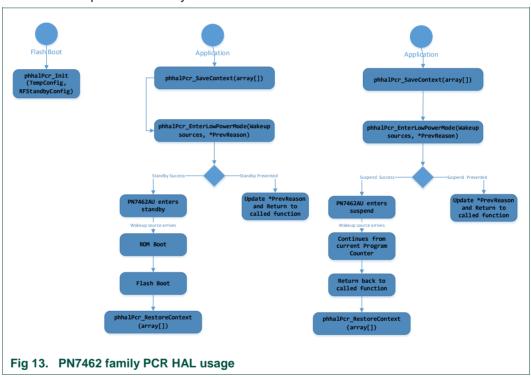

#### 4.6 PN7462 family PCR HAL

The PN7462 family IC provides two low-power modes:

1. Standby mode

# 2. Suspend mode (only when USB interface is used)

The PCR HAL is primarily used to put the IC into one of these modes.

The *phhalPcr\_Init()* is used by the flash boot to initialize the temperature sensors and CLIF analog characteristics during standby mode. The *phhalPcr\_Init()* also takes as input a bitmap that indicates power down settings during IC suspend (USB suspend). The USB suspend performs these power-down settings as well as restores the settings when resuming.

**PN7462 family Software User Manual**

## 4.6.1 Wake-up sources and prevention reason

The FW configures the sources that would wake up the IC from standby or suspend state. The sources that could wake up the IC are tabulated below. Refer PCR\_WAKEUP\_CFG\_REG.

Table 18. Wake-up source

| Wake-up source    | FW configuration                                                                                                                                                                                                                                        |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WUC (WUC_VALUE)   | The FW configures the WUC_VALUE and enable this source so that the IC wakes up every WUC_VALUE time period and performing polling operations                                                                                                            |

| RFLDT             | The FW enables this source so that the IC wakes up when an external RF is detected. If listen mode is <b>not</b> supported, as in the case of EMVCo reader, this source is disabled                                                                     |

| TEMP0 (CL sensor) | The FW enables it during flash boot initialization                                                                                                                                                                                                      |

| TEMP1 (CT sensor) | The FW enables it during flash boot initialization                                                                                                                                                                                                      |

| GPIO              | The FW enables this source if any peripheral is connected to GPIO that wakes up the IC; for example, Keypad                                                                                                                                             |

| PVDD_LIMITER      | If internal LDO is used to generate PVDD, the FW enables this source. While in standby, if there is a fault causing more current draw from PVDD LDO, then IC is woken up. But no functionality is possible because pad voltage is <b>not</b> available. |

| CT_PR             | The FW enables this source if a CT card has to be detected while in standby.                                                                                                                                                                            |

|                   | If WUC is also enabled, there is a possibility that IC always wakes up because of WUC and CT presence is never detected.                                                                                                                                |

| INT_AUX           | The FW enables this source if a CT card connected to a TDA (through IO-AUX) has to be detected while in standby                                                                                                                                         |

| TVDD_MON          | If internal LDO is used to generate TVDD, the FW enables this source. While in standby, if there is a fault causing more current draw from TX LDO, then IC is woken up. No RF functionality may be possible.                                            |

| VBUS_LOW          | The FW enables this source if for example, the device is a battery-operated one and a drop in VBUS is detected while in standby so that indication can be provided to users.                                                                            |

Note: Not all PN7462 family members have CT interface

The FW uses the EEPROM structure *phhalPcr\_WakeUpConfig\_t* to configure required wake-up sources depending on the requirement.

## **PN7462 family Software User Manual**

Table 19. EEPROM parameters for PCR HAL - Wake-up config

Wake-up Sources see also phhalPcr WakeUpConfig t

| Type | Field name       | Default value | Description                                                                                                             |  |

|------|------------------|---------------|-------------------------------------------------------------------------------------------------------------------------|--|

| u16  | wWakeUpTimerVal  | 300           | Timer value for the wake-up in milliseconds                                                                             |  |

| u8   | bEnableHIFWakeup | 0             | Flag to know the host interface wake-up 0: Disabled 1: Enabled                                                          |  |

| u8   | bl2CAddr         | 0x28          | I <sup>2</sup> C address if the wake-up is configured for HIF                                                           |  |

| u8   | bWakeUpTimer     | 1             | Flag to enable the wake-up timer as wake-up source 0: Disabled 1: Enabled                                               |  |

| u8   | bWakeUpRfLdt     | 0             | Flag to enable the RfLdt as wake-up source 0: Disabled 1: Enabled                                                       |  |

| u8   | bWakeUpPvddLim   | 1             | Flag to enable PVDD current limitation as wake-up source when it goes below the lower threshold 0: Disabled 1: Enabled  |  |

| u8   | bWakeUpCtPr      | 1             | Flag to enable CT presence as wake-up source when it goes below the lower threshold 0: Disabled 1: Enabled              |  |

| u8   | bWakeUpIntAux    | 0             | Flag to enable PVDD Auxiliary interrupt as wake-up source when it goes below the lower threshold 0: Disabled 1: Enabled |  |

| u8   | bWakeUpTvddMon   | 0             | Flag to enable TVDD Monitoring as wake-up source when it goes below the lower threshold 0: Disabled 1: Enabled          |  |

| u8   | bWakeUpGpio      | 0             | Flag to enable GPIO as wake-up source when it goes below the lower threshold 0: Disabled 1: Enabled                     |  |

Note: Not all PN7462 family members have CT interface

For a detailed parameter description, and parameter addresses in the EEPROM refer to the EEPROM description [2] file.

If the PN7462 family IC is **not** able to go to standby or suspend mode due to some reasons such as ongoing transaction in the interfaces, the HW provides the reason.

The phhalPcr\_ApplyLowPower() is used to make the PN7462 family IC to enter standby or suspend mode. The first parameter in the phhalPcr\_ApplyLowPower() is used to configure the wake-up sources and the second parameter gets the reason for prevention, if any.

Note: If standby is successful, this API will never back. If suspend is successful, this API returns back when the IC resumes because of any wake-up source (including USB host initiated resume).

#### **PN7462 family Software User Manual**

## 4.6.2 Context saving

The PCR HW in PN7462 family product provides eight general-purpose registers which are reserved during standby (PCR\_GPREG0\_REG - PCR\_GPREG7\_REG). An application may use *phhalPcr\_SaveContext()* to save seven DWORDs before entering standby. After waking up, it may use *phhalPcr\_RestoreContext()* to retrieve the saved DWORDs. The API allows to save seven DWORDs only since PCR\_GPREG0\_REG is internally used by the HALs.

## 4.6.3 Power down settings during USB suspend mode

The customer can add or delete this configuration according to the specification and board connections. An application may use phhalPcr\_ReducePowerConsumption() API to apply this power down settings. Refer <u>Table 9</u>

Table 20. PWD settings during USB suspend mode

| Bit    | Description                                                               |

|--------|---------------------------------------------------------------------------|

| Bit 0  | pull down GPIO pad 1                                                      |

| Bit 1  | pull down GPIO pad 2                                                      |

| Bit 2  | pull down GPIO pad 3                                                      |

| Bit 3  | pull down GPIO pad 4                                                      |

| Bit 4  | pull down GPIO pad 5                                                      |

| Bit 5  | pull down GPIO pad 6                                                      |

| Bit 6  | pull down GPIO pad 7                                                      |

| Bit 7  | pull down GPIO pad 8                                                      |

| Bit 8  | pull down GPIO pad 9                                                      |

| Bit 9  | pull down GPIO pad 10                                                     |

| Bit 10 | pull down GPIO pad 11                                                     |

| Bit 11 | pull down GPIO pad 12                                                     |

| Bit 12 | pull down ATX A pad                                                       |

| Bit 13 | pull down ATX B pad                                                       |

| Bit 14 | pull down ATX C pad                                                       |

| Bit 15 | pull down ATX D pad                                                       |

| Bit 16 | pull down INT_AUX pad                                                     |

| Bit 17 | pull down IO_AUX pad                                                      |

| Bit 18 | pull down CLK_AUX pad                                                     |

| Bit 19 | pull down all SPIM pads (SCK, NSS, MOSI, MISO)                            |

| Bit 20 | pull down all IICM pads (SCL, SDA)                                        |

| Bit 21 | Disable CT clock                                                          |

| Bit 22 | Disable CLIF modules and clocks (disable CLIF_PLL, power down submodules) |

configuration in phhalPcr ReducePowerConsumption() API.

# Bit Description Bit 23 GSN value in standby mode set to standby value

**PN7462 family Software User Manual**

Note: If an GPIO pin is used as wake-up source from USB suspend mode, then GPIO pin should be configured as input and pulled down. The corresponding GPIO bit position in

dwPwrDownSettings in EEPROM should be set to 0 to prevent overwriting GPIO pad

## 4.6.4 Register IRQ callback

The PCR HW events are asynchronous. An application may wish to register for specific asynchronous events such as VBUSP (for DCDC LDO) monitor status, PVDD LDO current limiter irq take necessary action.

## 4.7 PN7462 family PMU HAL

The PN7462 family product provides three LDOs:

- 1. TXLDO for CLIF transmitter

- 2. PVDD LDO for generating 3.3 V pad voltages (requirement for USB)

- DC-DC LDO for CT communication (applicable for PN7462 family members with CT interface)

#### **PN7462 family Software User Manual**

The PMU HAL provides interfaces for application to configure these LDOs depending on the application use case.

#### 4.7.1 TXLDO HAL

The TXLDO is started in full power mode.

In full power mode, the TXLDO can be configured to provide an output voltage of 3.0 V/3.3 V/3.6 V/4.75 V.

Optionally, overcurrent detector can be enabled during its on-period.

The default boot from flash uses *phhalPmu\_TxLdoInit()* to configure these parameters (by reading values from the EEPROM). The API *phhalPmu\_TxLdoStart()* is used to start the TXLDO. Whenever the CLIF HW is **not** used (to reduce power consumption), the TXLDO can be stopped using the *phhalPmu\_TxLdoStop()* API.

For the use cases where the TXLDO output requirement is 4.5 V or 4.75 V, it is required to have 5 V at the input of TXLDO. It is checked by the application using phhalPmu\_TxLdo5VMonitor().

In the reference boot code and standby/suspend APIs provided by NXP uses the *phhalPmu\_TxLdoStart()* on boot up and before entering standby/suspend mode.

For system configuration, the system does not use internal TXLDO for TVDD. It uses an external LDO to connect to TVDD. The application shall set the information during initialization.

Note: If TXLDO is **not** used, HAL does not check if TVDD is available.

In case of external TVDD, TVDD\_IN supply must be stable before turning on the RF field. User application should ensure that TVDD\_IN supply is stable before turning ON RF field. The PN7462 includes two levels (4 V and 3.3 V) voltage monitor for monitoring the voltage on the TVDD\_IN or VUP\_TX pins. Voltage Monitor can be configured to monitor voltage on either TVDD\_IN or VUP\_TX pins.

Two APIs "phhalPmu\_TxLdoMonitorEnable" and "phhalPmu\_TxLdoMonitorCheck" are provided to configure and Check Monitor. These APIs should be use by User application to ensure TVDD\_IN Supply is stable before turning ON RF field.

#### 4.7.2 DC-to-DC LDO HAL

This section is applicable for PN7462 family members with CT interface. The DC-to-DC LDO is primarily used to drive the VCC LDO either in the follower mode or in doubler mode, depending on the configuration discussed in <u>Table 21</u>.

Table 21. DC-to-DC LDO mode configuration

| Class of card | Voltage @VBUSP | DC-to-DC LDO mode |

|---------------|----------------|-------------------|

| Class A       | > 3 V          | doubler           |

| Class B       | < 3.9 V        | doubler           |

|               | > 3.9 V        | follower          |

## **PN7462 family Software User Manual**

| Class of card | Voltage @VBUSP | DC-to-DC LDO mode |  |

|---------------|----------------|-------------------|--|

| Class C       | > 2.7 V        | follower          |  |

The DC-to-DC LDO API <u>phhalPmu\_DcdcLdoStart()</u> is used to perform the above configuration, depending on the class of card being used for activation. The CT HAL internally uses this API and the application does not need to use this API directly.

The <u>phhalPmu\_DcdcLdoStart()</u> also enables the voltage monitor at VBUSP pin, depending on the class of card and the mode of operation. If the VBUSP drops below the threshold voltage, an interrupt is generated. The interrupt performs asynchronous deactivation of the CT and notifies the application.

In FW deactivates CT, the function phhalPmu\_DcdcLdoStop() is called automatically.

Table 22. VBUSP threshold

| Class of card         | VBUSP monitor threshold | Typical action on reaching below threshold       |

|-----------------------|-------------------------|--------------------------------------------------|

| class A doubler mode  | 3 V                     | SW deactivates CT                                |

| class B follower mode | 3.9 V                   | SW deactivates CT and reactivate in doubler mode |

| class B doubler mode  | 2.7 V                   | SW deactivates CT                                |

| class C follower mode | 2.7 V                   | SW deactivates CT                                |

#### 4.7.3 PVDD LDO HAL

The PN7462 family IC provides an internal LDO for generating 3.3 V pad voltage. According to the system requirement of using internal or external LDO, the HW configuration is different. Ideally, if an internal LDO is used, the ROM boot identifies the configuration and starts the PVDD LDO.

The PVDD LDO APIs are typically used during USB suspend scenario. Here, the PVDD LDO is put to low power using *phhalPmu\_PvddLdoLowPower()* and reverted to full power using *phhalPmu\_PvddLdoStart()*.

The PVDD LDO HAL API also provides *phhalPmu\_PvddLdoStop()* even though it is **not** used.

# 4.7.4 Register IRQ callback

The PMU HW events are asynchronous. An application may wish to register for specific asynchronous events such as DC-to-DC Overload, TxLDO overcurrent etc. and take necessary action.

## **PN7462 family Software User Manual**

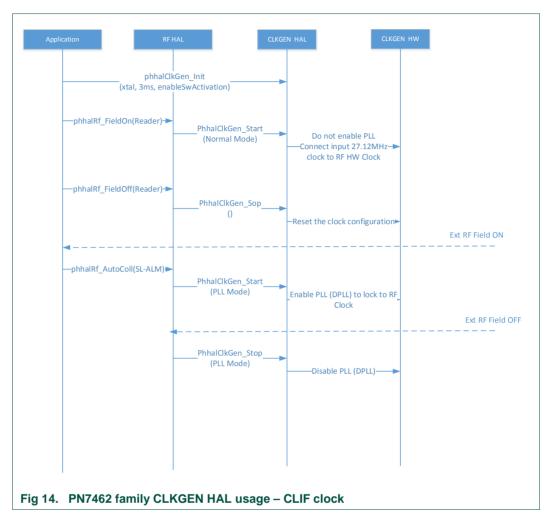

# 4.8 PN7462 family CLKGEN HAL

In PN7462 family IC, two clock frequencies are required:

- 1. 27.12 MHz for CLIF, CT, I2CM, SPIM, and HSU

- 2. 48 MHz for USB

The system design allows two clock sources to be connected to the crystal pins of the PN7462 family IC. They are:

- 1. 27.12 MHz crystal

- 2. 27.12 MHz external clock source such as digital clock or on-board resonator

For the clock source of 27.12 MHz crystal, PN7462 family IC contains a crystal oscillator that starts automatically upon booting. Depending on the crystal, there is some delay until the oscillator is stable. If the automatic activation fails, the oscillator can be SW activated.

Application configures the above options with the phhalClkGen\_Init() API.

For the external clock source of 27.12 MHz, ideally the crystal oscillator can be shutdown.

#### 4.8.1 CLIF clock

The PN7462 family IC also contains a PLL that generates a stable 27.12 MHz clock. The PLL can be used for the following two reasons:

- 1. The PLL is used if the external digital/resonator clock source generates a frequency other than 27.12 MHz. It is **not** supported in this product.

- 2. For single-loop ALM use case, DPLL is used to lock to RF clock. It is supported in this product.

Hence for reader modes, active modes and card mode (PLM), PLL is not started and in card mode (SL-ALM), PLL is started and is locked to RF clock.

This functionality is achieved by calling *phhalClkGen\_ClifClockStart()* API. The RF HAL internally uses these APIs and the application use them.

#### **PN7462 family Software User Manual**

### 4.8.2 USB clock

The USB requires a bus clock of 48 MHz. This clock is derived from the input source of 27.12 MHz, by appropriate configuration of USB PLL. During USB HAL initialization, the *phhalClkGen\_UsbClockStart()* is called to lock the PLL to 48 MHz. Similarly, during USB suspend or USB HAL de-initialization, *phhalClkGen\_UsbClockStop()* is called.

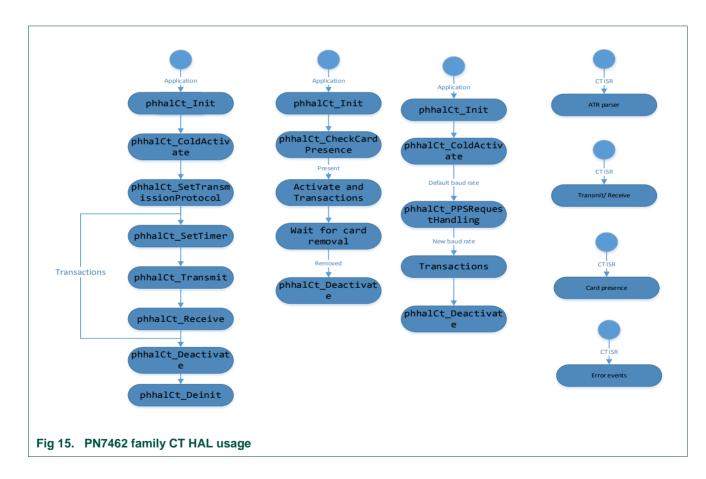

## 4.9 PN7462 family CT HAL

The CT HAL provides the following features.

Note: Applicable to the PN7462 family derivatives with CT.

#### 4.9.1 Profiles

The CT protocol library can be configured with two different profiles, namely ISO7816 or EMVCo profile. The configuration can be done during the protocol initialization. The card

## **PN7462 family Software User Manual**

activation and the transactions are performed according to the selected profile. It is not recommended to switch the profile in between card activation or transaction.

## 4.9.2 Set Config

In this version of FW, the profile can be changed at run-time using SetConfig API that enables/disables the EMV profile.

## 4.9.3 Card presence check

The card presence in the slot can be checked using this feature. This feature provides the card presence or absence in the main slot.

#### 4.9.4 Cold activation

- Cold activation in class A or class B or class C