# eTPU RDC and RDC Checker User Guide

# Contents

| Chapter 1 Product Description                  | 3  |

|------------------------------------------------|----|

| Chapter 2 Integrating and Building the Product |    |

| Chapter 3 Configurations                       | 25 |

| Chapter 4 APIs                                 | 28 |

| Chapter 5 Demos and Application Notes          | 31 |

| Chapter 6 References                           | 32 |

# Chapter 1 Product Description

This user guide provides detailed description of eTPU RDC function implementation as well as host RDC Checker. The user guide provides complete guidance for configurations and usage of both SW products to ensure safety operation. The SW described within this manual is applicable to devices containing Enhanced Timer Processing Unit (eTPU, eTPU2 and eTPU2+).

Acronyms and terms used in the document are listed below.

#### Table 1. Acronym and definition

| Acronym | Definition                              |

|---------|-----------------------------------------|

| RDC     | Resolver to Digital Converter           |

| eTPU    | Enhanced Time Processing Unit           |

| SDADC   | Sigma-Delta Analog to Digital Converter |

| АТО     | Angle-Tracking Observer                 |

| SRF     | Safety Runtime Framework                |

| API     | Application Interface                   |

| PIT     | Periodic Interrupt Timer                |

| HSR     | Host Service Request                    |

| ISR     | Interrupt Service Request               |

| PWM     | Pulse Width Modulation                  |

## 1.1 Resolver Digital Interface (RESOLVER)

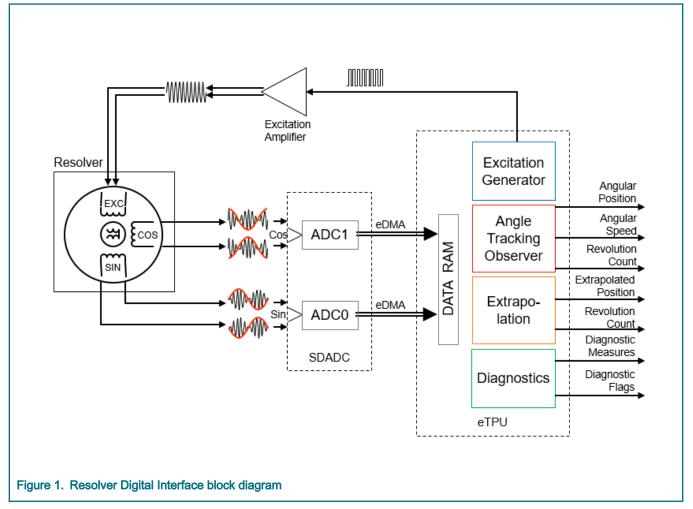

The Resolver Digital Interface eTPU function (RESOLVER) uses one eTPU channel to generate a 50% duty-cycle PWM output signal to be passed through an external low-pass filter and used as a resolver excitation signal. In the resolver position sensor, this excitation signal is modulated by sine and cosine of the actual motor angle. The feedback Sine and Cosine signals are sampled by an on-chip ADC and the conversion results can be transferred to eTPU DATA RAM by eDMA. eTPU function RESOLVER can then process the digital samples of resolver output signals. Motor angular position, angular speed, a revolution counter, and diagnostics are results of the Sine and Cosine feedback signal processing.

Processing of the feedback signals is executed on a separate channel. Another channel is used to perform linear extrapolation of the last updated position from ATO to any other time. Optionally, another eTPU channel can be used to process diagnostics either on the same eTPU engine after the feedback signal processing is finished (see the channel assignment example in Table 3) or on the other eTPU engine in parallel to the motor angle and speed calculation, see Table 4. This enables the CPU application to read the new motor angle and, at the same time, check the diagnostic results to ensure the motor angle is correct.

As an alternative to diagnostics running on eTPU Resolver function there is the RDC Checker, an external checker running on CPU. This option allows eTPU Resolver to be a part of ASIL-D decomposition, where the eTPU Resolver function (QM(D)) runs in Non-Trusted Environment (NTE) and the RDC Checker (ASIL-D(D)) in Trusted Environment (TE)

Features:

- Generation of excitation signal a 50% PWM wave to be filtered externally.

- · Adaptive phase control of the excitation signal.

- · Motor angle and speed tracking

- · Extrapolation of the resulting angle to a defined time-position

- Diagnostic measurements (optionally running in parallel on the other eTPU engine)

- · Diagnostic flag settings (optionally running in parallel on the other eTPU engine)

## 1.1.1 Excitation signal generation and adaptive phase control

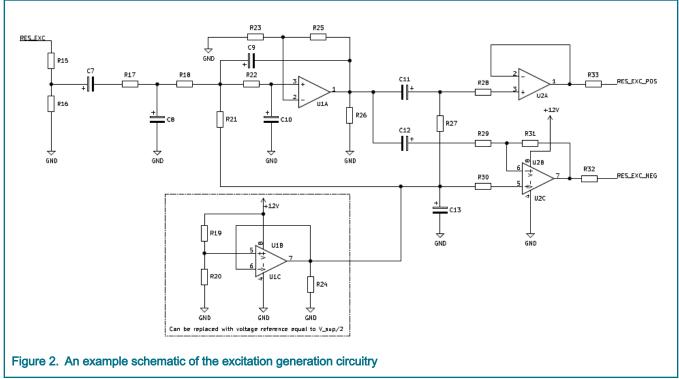

The Resolver Digital Interface eTPU function generates a square output wave of a defined period which is intended to be filtered and gained by an external circuitry to get the excitation sine wave. An example of the external circuitry schematic for filtration of

10 kHz output square signal to gain sine-wave resolver excitation of the same frequency is shown in the following figure. Note that this is just a simplified example, not all the connections are shown.

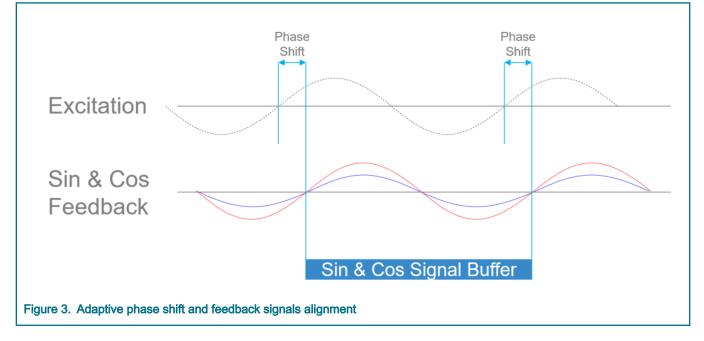

The adaptive control of the excitation signal phase is enabled by setting the bit

FS\_ETPU\_RESOLVER\_OPTIONS\_EXC\_ADAPTATION\_ON in *resolver\_config.options*. Using a PI controller (*exc\_p\_gain*, *exc\_i\_gain*), the excitation signal phase is adjusted so, that the zero crossings of the Sine and Cosine feedback signals are at the required position and the signals are phase-aligned in the input signal buffers, see the following figure.

## 1.1.2 Sine and Cosine feedback signal digitization

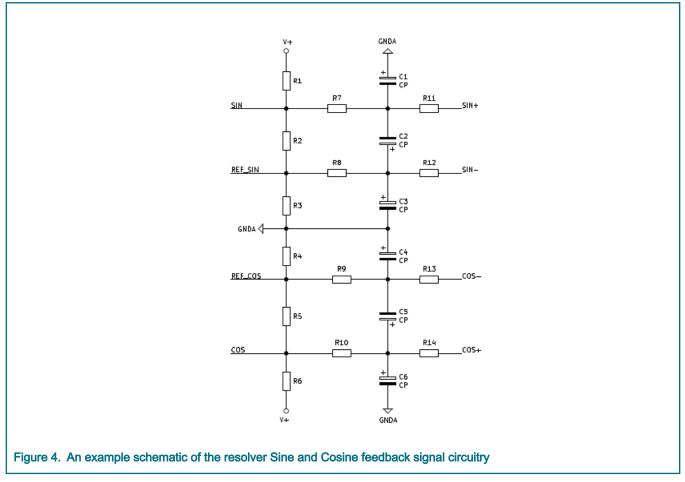

The Sine and Cosine analog feedback signals need to be converted to a digital representation and transferred to eTPU DATA RAM. This should be done independently of the CPU using an on-chip ADC and eDMA. Although any of the ADC modules can be used, the described configuration adopts the Sigma-Delta ADC (SDADC).

Differential ADC inputs are used, which simplifies the input circuitry. The following figure shows an example of the external circuitry schematic.

Two SDADC modules are used to continuously sample the Sine and Cosine signals in parallel. They are configured to obtain 32 samples of each signal per period. The following table shows the configuration for a 10 kHz excitation signal and a 320 kHz sampling frequency in detail.

### Table 2. SDADC Configuration.

| Configuration Item         | Value                                                 |

|----------------------------|-------------------------------------------------------|

| SDADC clock                | 200 MHz / 13 = 15.38 MHz (available range 4 – 16 MHz) |

| ADC decimation rate        | 24                                                    |

| Resulting output data rate | 200 MHz / 13 / (2 * 24) = 320,512.8 Hz                |

| Input mode                 | differential (recommended)                            |

| High-pass filter           | enabled                                               |

Table continues on the next page ...

### Table 2. SDADC Configuration. (continued)

| Configuration Item       | Value                |

|--------------------------|----------------------|

| FIFO size                | 16 words             |

| FIFO threshold           | 16 words             |

| DMA request on FIFO full | selected and enabled |

The ADC generates a DMA request every time when 16 samples are ready in the FIFO. These 16 samples correspond to either the first or the second half-period of the input signal. The DMA transfers those samples to the eTPU DATA RAM, either to the first or the second half of the signal buffer, and subsequently evokes the eTPU to process the new data. This is done by linking another DMA channel which transfers a constant value to the eTPU Host Service Request (HSR) register. Then eTPU processes the HSR. Different HSRs are used for the first and for the second half-period:

- FS\_ETPU\_RESOLVER\_HSR\_UPDATE\_1ST

- FS\_ETPU\_RESOLVER\_HSR\_UPDATE\_2ND

Altogether, three DMA channels are used – two channels to transfer the ADC data of Sine and Cosine signals, and one channel to transfer the HSRs. The following table shows eDMA configuration in detail.

#### Table 3. eDMA Configuration

| Configuration Item                     | Sine ADC FIFO DMA<br>channel     | Cosine ADC FIFO DMA<br>channel        | Linked HSR DMA channel                                                                                          |

|----------------------------------------|----------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Source address                         | &SDADC_x.CDR.R                   | &SDADC_y.CDR.R                        | &link_const[0]                                                                                                  |

|                                        |                                  |                                       | const uint32_t link_const[] =<br>{FS_ETPU_RESOLVER_HSR_<br>UPDATE_1ST,<br>FS_ETPU_RESOLVER_HSR_<br>UPDATE_2ND}; |

| Destination address                    | resolver_instance<br>signals_pba | resolver_instance<br>signals_pba + 64 | &ETPU.CHAN[resolver_instan ce.chan_num_exc].HSRR.R                                                              |

| Source transfer size / modulo          | 32-bits / 0 bytes                | 32-bits / 0 bytes                     | 32-bits / 0 bytes                                                                                               |

| Destination transfer size / modulo     | 32-bits / 64 bytes               | 32-bits / 64 bytes                    | 32-bits / 0 bytes                                                                                               |

| Source address offset                  | 0 bytes                          | 0 bytes                               | 4 bytes                                                                                                         |

| Destination address offset             | 4 bytes                          | 4 bytes                               | 0 bytes                                                                                                         |

| Minor loop byte count                  | 64 bytes                         | 64 bytes                              | 4 bytes                                                                                                         |

| Major loop iteration count             | 2                                | 2                                     | 2                                                                                                               |

| Last source address adjustment         | 0 bytes                          | 0 bytes                               | -8 bytes                                                                                                        |

| Last destination address<br>adjustment | -128 bytes                       | -128 bytes                            | 0 bytes                                                                                                         |

Table continues on the next page ...

| Configuration Item         | Sine ADC FIFO DMA<br>channel | Cosine ADC FIFO DMA channel | Linked HSR DMA channel |

|----------------------------|------------------------------|-----------------------------|------------------------|

| Channel to channel linking | disabled                     | enabled                     | disabled               |

| Linked channel             | -                            | HSR DMA channel             | -                      |

#### Table 3. eDMA Configuration (continued)

## 1.1.3 Resolver angle and speed tracking

Having the Sine and Cosine feedback signals in the signal buffer, the actual resolver angle could theoretically be calculated using the arcustangent function after signal demodulations.

$$\theta = \arctan\left(\frac{\sin(\theta)}{\cos(\theta)}\right)$$

where  $sin(\theta)$  and  $cos(\theta)$  are the demodulated resolver feedback signals.

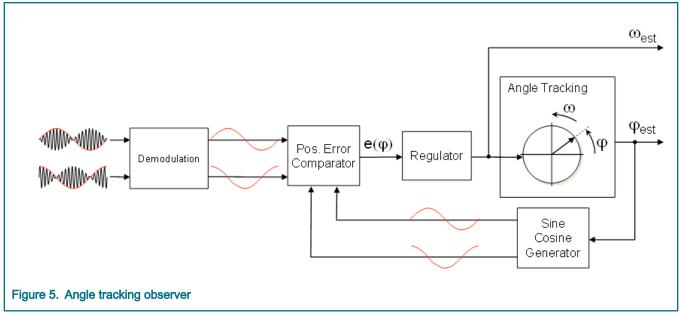

This straightforward way has several disadvantages, as a long calculation time or a low noise immunity. Due to those reasons the Angle Tracking Observer (ATO) is introduced. The ATO tracks angular motor speed and calculates actual motor angle using a prediction and correction approach. The following figure shows the block diagram of this algorithm.

The ATO consists of the following blocks:

- Demodulation: The excitation signal is modulated by Sine and Cosine of the motor angle by the resolver. The

Demodulation block extracts the modulation signal out of the excitation (carrying) signal. This is done by oversampling the

modulated excitation signal (sampling rate 320.5128 kHz) and thus obtaining 32 samples per period, 16 samples per halfperiod respectively. The half period is being demodulated by factor of the carrier signal (sine) and median filter is used to

determine the modulation signal amplitude (resolver angle sine and cosine). Median filter is suppressing the impulse

noise.

- Position Error Comparator: This block takes the Sine and Cosine of the motor angle measured from the resolver feedback signals and the Sine and Cosine calculated from the motor angle estimated by the ATO algorithm. Using those inputs, an angle error is calculated. The calculation is based on the trigonometric identity.

$sin(\alpha - \beta) = sin(\alpha)cos(\beta) - cos(\alpha)sin(\beta)$

For small angles following simplification can be applied.

sin(ɛ) =≌ɛ

For bigger angles a convergency of the ATO algorithm can be proofed. As a result, the position error is calculated.

$e(\theta) = \theta - \theta_{est} \cong sin(\theta)cos(\theta_{est}) - cos(\theta)sin(\theta_{est})$

Where  $sin(\theta)$  and  $cos(\theta)$  are the demodulated resolver feedback signals,  $cos(\theta_{est})$  and  $sin(\theta_{est})$  are calculated sine and cosine values of the ATO motor angle output, and is the resulting motor angle error.

- Regulator: The Regulator takes the position error as an input and returns estimated motor speed as an output. A 24-bit

fractional PI controller is implemented for this task. The Excel file Resolver ATO PI-gains.xlsx, which is included in the

attached software package, might help to set the PI controller gains.

- Angle Tracking: The Angle Tracking block adjusts the actual motor angle using the updated motor speed. As a result, the estimated motor angle is returned.

There are two Angle Tracking Observer updates per period, separately using the first and the second half-period of the Sine and Cosine signals.

## 1.1.4 Extrapolation

The calculated motor angle corresponds to the time position of the half-period center. In a motor control application, the motor angle reading should correspond in time to the phase current readings. To achieve this, there is a feature to linearly extrapolate the calculated motor angle to another time position, using the actual motor speed.

The angle and speed are extrapolated to the time when the extrapolation is triggered. It can be triggered by:

- · Host service request from application

- · Link from other eTPU channel

- · Input transition detection (rising/falling edge)

To enable calculation of the extrapolated angle values the FS\_ETPU\_RESOLVER\_OPTIONS\_EXTRAPOLATION\_ON has to be configured in *resolver\_config.options*, The API function *fs\_etpu\_resolver\_get\_outputs\_extrapolated()* can be called to read the extrapolated results.

## 1.1.5 Diagnostics

There are two ways how the operation of the eTPU Resolver can be checked. The first one is to run diagnostics on eTPU as described in eTPU diagnostics. The second option is to use RDC (Resolver-to-Digital-Converter) checker, see description in RDC checker.

#### 1.1.5.1 eTPU diagnostics

The Resolver Diagnostics on eTPU can run in parallel to the motor position processing on the other eTPU engine or after the motor position processing on the same engine. See the following tables.

| Channel       | Assignment | Note                                                                  |

|---------------|------------|-----------------------------------------------------------------------|

| chan_num_exc  | 9          | Excitation signal generation runs on eTPU A channel 9.                |

| chan_num_ATO  | 8          | Motor position processing runs on eTPU A channel 8.                   |

| chan_num_diag | 10         | Diagnostics run after motor position processing on eTPU A channel 10. |

#### Table 4. RESOLVER channel assignment - Example 1

| Channel       | Assignment | Note                                                                                 |

|---------------|------------|--------------------------------------------------------------------------------------|

| chan_num_exc  | 9          | Excitation signal generation runs on eTPU A channel 9.                               |

| chan_num_ATO  | 8          | Motor position processing runs on eTPU A channel 8.                                  |

| chan_num_diag | 3+64       | Diagnostics run <b>in parallel</b> to motor position processing on eTPU B channel 3. |

#### Table 5. RESOLVER channel assignment – Example 2

The Resolver Diagnostics are enabled by setting following bits in resolver\_config.options

- FS\_ETPU\_RESOLVER\_OPTIONS\_DIAG\_MEASURES\_ON

- FS\_ETPU\_RESOLVER\_OPTIONS\_DIAG\_FLAGS\_ON.

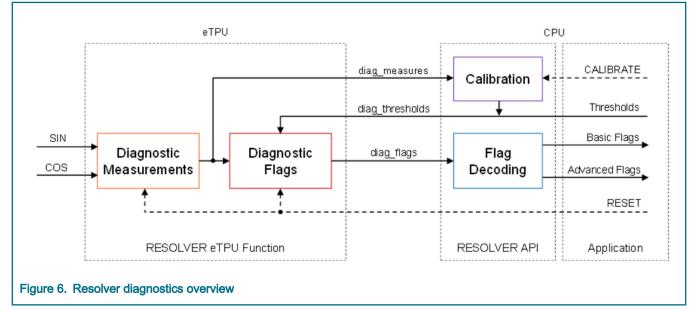

The diagnostics processing is handled partly by the eTPU function and partly by the CPU API. On the eTPU site, the Sine and Cosine feedback signals are diagnosed in two phases:

- · Diagnostic Measurements signal properties are measured

- · Diagnostic Flags flags are set upon comparing the measured values against the thresholds

On the CPU site, additional flag decoding can be done. This part is somewhat dependent on the external circuitry (excitation amplifier, input filters) and that is why this part is done within API, so that the user can easily modify the code according to the need.

The diagnostic thresholds can be provided by the CPU application as manually configured constants, or thresholds can be determined from the measured signal properties by a call of *fs\_etpu\_resolver\_diag\_calibrate()* API function. Passing at least one full motor revolution guaranties enough data for that automatic calibration. The application also needs to make sure the input signals are not corrupted before calling the calibration.

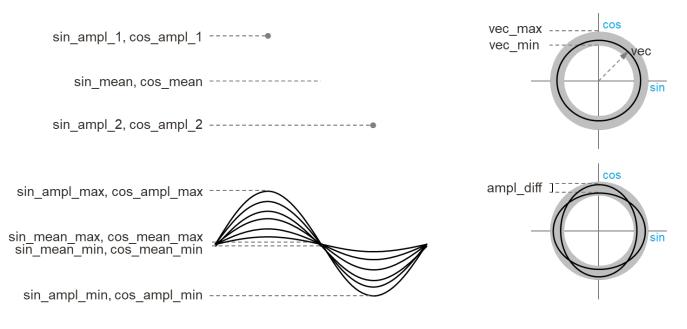

Both the diagnostic measurements and diagnostic flags include some actual and some cumulative values. In order to reset and restart the measurement and the flag setting, the API function *fs\_etpu\_resolver\_diag\_reset()* can be called. The diagnostic measures are shown in the following figure and RESOLVER diagnostic flags lists all the values which are computed by the diagnostic measurements.

### Figure 7. Resolver diagnostic measures

**Product Description**

NOTE

The resolver feedback signals have to be conditioned so that the amplitudes being displayed on the unitary circle of both sine and cosine are within the range from  $\pm 0.3$  to  $\pm 0.8$ . The upper limit should not be exceeded in case diagnostics are planned to be used to allow the excursion of the signals to be detected when the unitary circle is distorted due to shortcuts and signal losses.

#### Table 6. RESOLVER diagnostic measures

| resolver_diag_measures_t structure<br>member |              | Description                                                                                                                                                   |

|----------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sin_ampl_1                                   | cos_ampl_1   | Amplitude of the first, positive, half period                                                                                                                 |

| sin_ampl_2                                   | cos_ampl_2   | Amplitude of the second, negative, half period                                                                                                                |

| sin_ampl_min                                 | cos_ampl_min | The lowest amplitude ever detected                                                                                                                            |

| sin_ampl_max                                 | cos_ampl_max | The highest amplitude ever detected                                                                                                                           |

| sin_mean                                     | cos_mean     | The signal mean value (DC component)                                                                                                                          |

| sin_mean_min                                 | cos_mean_min | The lowest mean value ever detected                                                                                                                           |

| sin_mean_max                                 | cos_mean_max | The highest mean value ever detected                                                                                                                          |

| v                                            | ec           | Square value of a vector formed by sin and cos amplitudes as its orthogonal components                                                                        |

| vec_min                                      |              | The lowest value of the square vector value ever detected                                                                                                     |

| vec_max                                      |              | The highest value of the square vector value ever detected                                                                                                    |

| ampl_diff                                    |              | The difference between the highest amplitude ever detected of one signal and the lowest amplitude ever detected of the other signal – unit circle deformation |

The following table lists all the thresholds against which the diagnostic measures are compared.

Table 7. RESOLVER diagnostic thresholds

| resolver_diag_thresholds_t<br>structure member | Description                                        |

|------------------------------------------------|----------------------------------------------------|

| ampl_thrs                                      | The highest absolute amplitude value threshold     |

| mean_thrs                                      | The highest absolute mean value threshold          |

| vec_min_thrs                                   | The lowest square vector threshold                 |

| vec_max_thrs                                   | The highest square vector threshold                |

| ampl_diff_thrs                                 | The highest sin/cos amplitude difference threshold |

| ato_angle_err_thrs                             | The highest ATO angle error threshold              |

| ato_speed_thrs                                 | The highest ATO speed threshold                    |

The following table lists all diagnostic flags and conditions under which the flags are set.

### Table 8. RESOLVER diagnostic flags

| resolver_diag_flags_t structure<br>member bits |          | Condition                           | Description                                                   |

|------------------------------------------------|----------|-------------------------------------|---------------------------------------------------------------|

| SIN_AMPL                                       | COS_AMPL | ampl_1/2  > ampl_thrs               | The amplitude is higher than the threshold                    |

| SIN_MEAN                                       | COS_MEAN | mean  > mean_thrs                   | The signal mean value is higher than the threshold            |

| VEC                                            | _MIN     | vec < vec_min_thrs                  | The square vector is lower than the threshold                 |

| VEC.                                           | _MAX     | vec > vec_max_thrs                  | The square vector is higher than the threshold                |

| AMPL                                           | DIFF     | ampl_diff > ampl_diff_thrs          | The sin/cos amplitude difference is higher than the threshold |

| ATO_ANGLE_ERR                                  |          | ato.angle_err  > ato_angle_err_thrs | The ATO angle error is higher than the threshold              |

| ATO_SPEED                                      |          | ato.speed  > ato_speed_thrs         | The ATO speed is higher than the threshold                    |

The eTPU runs the diagnostics every time when the new inputs are available (on every update). The CPU can run the flag decoding on a lower frequency, based on the application needs. No diagnostic flag can be missed, because any time a flag is detected, it remains to be set within the cumulative value.

### Table 9. RESOLVER actual and cumulative diagnostic flags

| resolver_diag_flags_t<br>structure member | Description                                                                        |

|-------------------------------------------|------------------------------------------------------------------------------------|

| actual                                    | Field of flags detected on the last update from the last diagnostic_measures data. |

Table continues on the next page ...

|                                                                                                                                                  | resolver_diag_flags_t<br>structure member | Description                                                                                                                                             |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| cumulative Field of cumulated flags. The actual flags are OR-ed to the cumulative flags of cumulative flags are cleared by reset of diagnostics. |                                           | Field of cumulated flags. The actual flags are OR-ed to the cumulative flags on every update. The cumulative flags are cleared by reset of diagnostics. |  |

#### Table 9. RESOLVER actual and cumulative diagnostic flags (continued)

The CPU can take the diagnostic flags provided by the eTPU function and use them to decode a higher level of diagnostics, Basic diagnostic flags and Advanced diagnostic flags. The following tables list those flags and describes the flag setting conditions. Note that these conditions might not be generally applicable for all types of external hardware circuitry. You can easily modify the flag setting condition in the API code according to the application specifics.

#### Table 10. Basic diagnostic flags

| resolver_diag_flags_basic bits | Condition                  | Description           |

|--------------------------------|----------------------------|-----------------------|

| LOS                            | VEC_MIN                    | Loss of Signal        |

| DOS                            | VEC_MAX or AMPL_DIFF       | Degradation of Signal |

| LOT                            | ATO_ANGLE_ERR or ATO_SPEED | Loss of Tracking      |

### Table 11. Advanced diagnostic flags

| resolver_diag_flags_<br>advanced bits | Condition – decoded in this order:       | Description                               |  |

|---------------------------------------|------------------------------------------|-------------------------------------------|--|

| SIN_DISCONNECT                        | SIN_MEAN and AMPL_DIFF and ATO_ANGLE_ERR | A wire of the SIN signal is disconnected. |  |

| COS_DISCONNECT                        | COS_MEAN and AMPL_DIFF and ATO_ANGLE_ERR | A wire of the COS signal is disconnected. |  |

| EXC_DISCONNECT                        | VEC_MIN and ATO_SPEED                    | A wire of the EXC signal is disconnected. |  |

| SIN_SHORT                             | SIN_MEAN and ATO_ANGLE_ERR               | A shortcut on the SIN signal wire.        |  |

| COS_SHORT                             | COS_MEAN and ATO_ANGLE_ERR               | A shortcut on the COS signal wire.        |  |

| EXC_SHORT VEC_MIN                     |                                          | A shortcut on the EXC signal wire.        |  |

## 1.2 RDC checker

RDC checker provides an alternative way of detecting eTPU Resolver functionality or input signals failure. The key difference is that the diagnostics are moved to CPU. eTPU Resolver function optionally records data for the external (meaning external to eTPU) checker. This functionality is enabled by setting following bits in *resolver\_config.options*:

FS\_ETPU\_RESOLVER\_OPTIONS\_RDC\_CHECKER\_ON

This option enables to Resolver function to log following data into a structure which is then transferred by DMA into a system RAM, where data are taken care of by RDC Checker. The structure of logged data at eTPU side is as follows:

- int24\_t sin\_8; /\* Sine sample on 8th position from signal buffer corresponding to peak of 1st half period\*/

- int24\_t sin\_24; /\* Sine sample on 24th position from signal buffer corresponding to peak of 2nd half period\*/

- int24\_t cos\_8; /\* Cosine sample on 8th position from signal buffer corresponding to peak of 1st half period\*/

- int24\_t cos\_24; /\* Cosine sample on 24th position from signal buffer corresponding to peak of 2nd half period\*/

- int24\_t sin\_16; /\* Sine sample on 16th position from signal buffer corresponding to zero crossing\*/

- int24\_t cos\_16; /\* Cosine sample on 16th position from signal buffer corresponding to zero crossing\*/

- fract24\_t ATO\_angle\_8; /\* ATO angle from 1st update\*/

- int24\_t timestamp\_8; /\* Timestamp for 1st update\*/

- fract24 t ATO angle 24; /\* ATO angle from 2nd update \*/

- int24\_t timestamp\_24; /\* Timestamp for 2nd update\*/

- fract24 t extrapolated angle; /\* Last Extrapolated angle value \*/

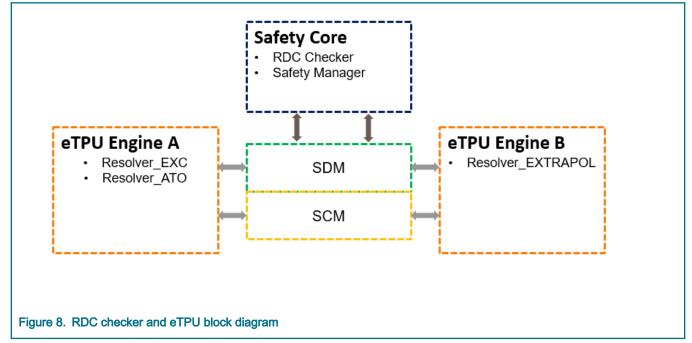

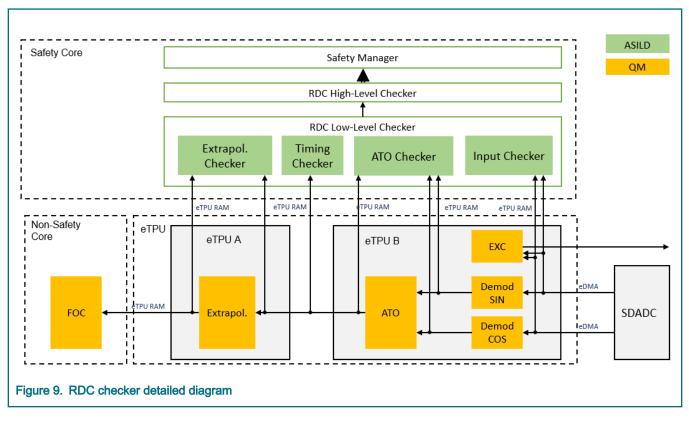

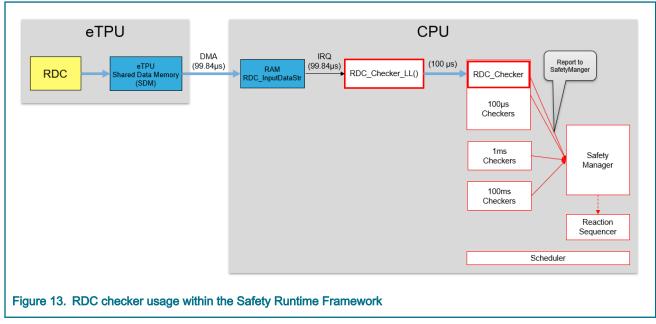

The block diagram of the RDC Checker and eTPU can be seen in the following figure. The RDC Checker can run either as a standalone checker or as a part of Safety Runtime Framework.

RDC Checker consists of four main parts, the detailed block diagram can be seen in the following figure:

- · Input signal checker

- ATO checker

- Extrapolation checker

- · Timing checker

## 1.2.1 Input signal checker

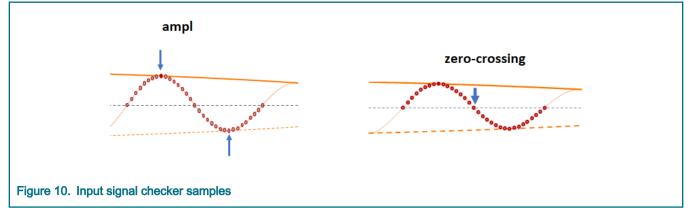

Input signal checker inspects the Resolver feedback signals that are to be processed by eTPU Resolver function. It checks the samples that are assumed to be the maximum amplitude points: sin[8], cos[8], sin[24] and cos [24] out of 32 point sample buffers. Also for the purpose of phase shift checks the samples of assumed zero crossings: sin[16] and cos[16]. See the following figure.

The checks that are performed within input signal checker part are listed in the following table. Test #1 ensures the SDADC and eDMA are not stucked. Amplitude range check is watching the amplitude does not over-cross the given threshold. Mean value check tests if there is any unwanted DC shift present in the feedback signals. Zero crossing check watches if the signal in the buffer is phase-shifted. Plausibility check ensures the samples fits into the unitary circle.

### Table 12. Input signal checks

| 1. | Check the sample values are | cos[8](n)<>cos[8](n-1) cos[24](n)<>cos[24](n-1) |

|----|-----------------------------|-------------------------------------------------|

|    | changing.                   | sin[8](n)<>sin[8](n-1) sin[24](n)<>sin[24](n-1) |

Table continues on the next page ...

| 2. | Check amplitude range.                       | sin[8]  < AMPL <sub>MAX</sub>  sin[24]  < AMPL <sub>MAX</sub><br> cos[8]  < AMPL <sub>MAX</sub>  cos[24]  < AMPL <sub>MAX</sub> |

|----|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 3. | Check signal mean value (DC shift).          | sin[8] + sin[24]  < MEAN <sub>MAX</sub><br> cos[8] + cos[24]  < MEAN <sub>MAX</sub>                                             |

| 4. | Check signal zero-crossing (phase shift)     | sin[16]  < ZC <sub>MAX</sub><br> cos[16]  < ZC <sub>MAX</sub>                                                                   |

| 5. | Check plausibility of samples (unit circle). | $sin^{2}[8] + cos^{2}[8] \cong const$<br>$sin^{2}[24] + cos^{2}[24] \cong const$                                                |

#### Table 12. Input signal checks (continued)

## 1.2.2 ATO checker

ATO checker uses the same samples as Input signal checker. It calculates the angle using an alternate method in order to avoid a systematic error. The angle is evaluated as arcus tangent of sine and cosine sample ratio for both half periods.

$$\theta \cong \arctan\left(\frac{\sin[8]}{\cos[8]}\right) \quad \theta \cong \arctan\left(\frac{-\sin[24]}{-\cos[24]}\right)$$

The samples sin[24] and cos[24] are negated to get correct angle value. The arcus tangent function is implemented as simplified polynomial approximation. The maximum error is 0.22deg. All four quadrands are handled. The resulting angle is then compared with eTPU ATO result.

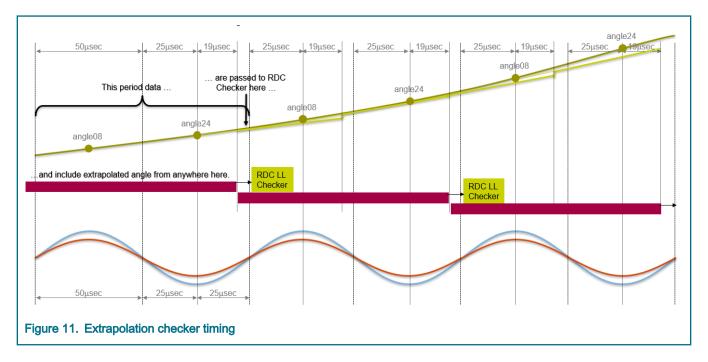

## 1.2.3 Extrapolation checker

Extrapolation checker reads and stores ATO outputs, angle updates per half period plus one extrapolated value. Checker use these samples and with a small delay checks whether the extrapolated angle fits between preceding and following ATO angle outputs. The acceptance range is extended for the case of small or zero speed when the preceding and the following ATO angles are almost the same.

## 1.2.4 Timing checker

The timing checker has two tasks, to check whether the timestapms corresponding to ATO angle updates are changing. This ensures that the ATO activity is not stucked.

timestamp[8](n) <> timestamp[8](n - 1)

timestamp[24](n) <> timestamp[24](n - 1)

The second task is to check whether the ATO updates are coming within expected time and thus samples are plausible.

$$timestamp[24](n) - timestamp[8](n) \sim rac{PERIOD}{2}$$

$timestamp[8](n) - timestamp[24](n-1) \sim rac{PERIOD}{2}$

# Chapter 2 Integrating and Building the Product

The development environment includes:

- MPC5777C EVB

- S32 Design Studio (S32DS)

- Optionaly Safety Runtime Framework (SRF)

To successfully run the RDC Checker the following steps needs to be performed:

- 1. Run eTPU Resolver function. The recommended channel usage is to run ATO channel on different engine than Extrapolation channel.

- 2. Enable RDC Checker functionality by configuring following option in resolver\_config\_t structure, FS\_ETPU\_RESOLVER\_OPTIONS\_RDC\_CHECKER\_ON

- 3. Include the RDC Checker source (*rdc\_checker.c/.h*) code into your project

- 4. Configure DMA to transfer data from eTPU RAM (located on *checker\_signal\_pba*) to *Rdc\_InputData* structure used by RDC Checker.

- 5. Configure the thresholds of RDC Checker in rdc\_checker.h

- 6. Enable DMA request from eTPU ATO channel and run RDC\_Checker\_LL() on IRQ from eDMA channel.

- 7. Use either *RDC\_Checker\_FaultStatus()* to read the RDC Checker results, or use the Safety Runtime Framwork (SRF) to integrate RDC Checker into a safety environment of application checkers and reactions.

The above mentioned steps are described in detail later in the sections.

## 2.1 How to get eTPU Resolver function up and running within CPU application

User has two options to get the eTPU Resolver binary, either download the compiled binary from NXP website (http:// www.nxp.com/etpu) or use eTPU source code and eTPU compiler. AN5374 describes in detail how to integrate the eTPU binary into the CPU application.

To configure the resolver function you have to modify etpu\_gct.c and etpu\_gct.h files.

## 2.1.1 Configuration of etpu\_gct.h

Channel assignment is performed as per the following steps. Resolver excitation and ATO function is running on engine A, Extrapolation feature (SAMPLE\_CHAN) is running on engine B. Diagnostics were set to engine B as well, but they are not used within this project.

• Configure both IRQ and DMA so both can be generated from ATO channel. DMA request is to transfer data from structure in eTPU data RAM to system RAM. IRQ is not essential for the RDC Checker functionality, it is used here within this

example application to read calculated outputs and states from resolver function as well as update data from config structure to the eTPU Resolver.

```

/ *______*

DEFINE INTERRUPT ENABLE, DMA ENABLE AND OUTPUT DISABLE

______*/

#define ETPU_CIE_A (1<<ETPU_RESOLVER_ATO_CHAN) /* enable interrupt on ETPU_RESOLVER_ATO_CHAN */

#define ETPU_DTRE_A (1<<ETPU_RESOLVER_ATO_CHAN) /* enable DMA request on ETPU_RESOLVER_ATO_CHAN */

#define ETPU_ODIS_A 0x0000000

#define ETPU_OPOL_A 0x0000000

#define ETPU_DTRE_B 0x0000000

#define ETPU_DIS_B 0x0000000

#define ETPU_OPOL_B 0x0000000

#define ETPU_OPOL_B 0x0000000</pre>

```

Enable global variable access to make the eTPU structures being visible outside the gct files to be accessible from main function.

| **                                                                       |

|--------------------------------------------------------------------------|

| GLOBAL VARIABLE ACCESS                                                   |

|                                                                          |

| */                                                                       |

| /* Global RESOLVER structures defined in etpu_gct.c */                   |

| <pre>extern struct resolver_instance_t resolver_instance;</pre>          |

| <pre>extern struct resolver_config_t resolver_config;</pre>              |

| extern struct resolver_outputs_t resolver_outputs_calculated;            |

| extern struct resolver_outputs_t resolver_outputs_extrapolated;          |

| <pre>extern struct resolver_outputs_t resolver_outputs_mechanical;</pre> |

| extern struct resolver_diag_measures_t resolver_diag_measures;           |

| extern struct resolver_diag_thresholds_t resolver_diag_thresholds;       |

| extern struct resolver_diag_flags_t resolver_diag_flags;                 |

| extern struct resolver_states_t resolver_states;                         |

|                                                                          |

· Declare function prototypes.

```

/ *-----*

FUNCTION PROTOTYPES

*/

int32_t my_system_etpu_init (void);

void my_system_etpu_start(void);

```

### 2.1.2 Resolver function configuration etpu\_gct.c

The Resolver function configuration itself is performed within *etpu\_gct.c* together with general engine configuration which is already part of etpu\_gct.c/h template files. This example configuration can be used as it is or you can modify as per your needs.

Apart from the files that are already present in template files include device specific file to specify eTPU data RAM frame plus Resolver API header file.

#### Integrating and Building the Product

```

#include "etpu\_utils\etpu_util.h" /* General C Functions for the eTPU */

#include "etpu\_etpu_set\etpu_set.h" /* eTPU function set code binary image */

#include "etpu\resolver\etpu_resolver.h" /* eTPU Resolver function API */

#include "include/mpc5777c_vars.h" /* Device specific header file */

```

eTPU engine configuration: Modify the predefined structure including parameters to configure eTPU engine. For a detailed

of the eTPU engine configuration please refer to eTPU Reference manual.

• Define Resolver instance structure: Uses definitions of particular channels from *etpu\_gct.h* for particular functionality assignment. Configure the Resolver function priority. Start offset parameter determines the first rising edge time of the Excitation signal – it is scheduled *start\_offset* number of TCR1 cycles after Resolver initialization. ADC delay is the parameter used to adjust the timestamp of ATO update. Start offset and ADC delay will be described in more detail in chapter Configurations. Channel parameter base address *cpba* can be configured for a particular address within the eTPU data memory (like in this case) or can be configured as 0, in that case *cpba* will be allocated automatically. The similar case applies for *signals\_pba* which stands for feedback signals parameter base address, a place within eTPU data RAM where sampled feedback signals are transferred from Sigma-delta ADCs FIFO using DMA requests. Parameter *checker\_signals\_pba* is address of structure where particular signals are stored for the purpose of RDC Checker. This should be configured as 0 and if RDC Checker option is enabled the address is automatically allocated on initialization.

NOTE

The *resolver\_instance\_t* structure can be modified only once at initialization. It is not a subject of change during the function runtime.

```

/*_____*

eTPU channel settings - RESOLVER

_____*

/** @brief Initialization of RESOLVER structures */

struct resolver instance t resolver instance :

{

ETPU RESOLVER EXC CHAN, /* chan num exc */

ETPU RESOLVER ATO CHAN, /* chan num ato */

ETPU RESOLVER DIAG CHAN, /* chan num diag */

ETPU RESOLVER SAMPLE CHAN, /* chan num sample */

ETPU RESOLVER ATO CHAN, /* chan num dma - etpuAl generate dma request on channel DMA A 28 */

FS ETPU PRIORITY HIGH, /* priority */USEC2TCR1(100), /*

start offset */USEC2TCR1(19), /* adc_delay */

0xC3FC8300, /* *cpba */ /* 0 for automatic allocation */

0xC3FC8600, /* *signals pba */ /* 0 for automatic allocation */

0 /* *checker signals pba - will be allocated automatically */

};

```

Define Resolver configuration structure: Use parameter *options* to configure intended functionality. *Excitation\_period* is configured to 99,84 µs – this is configured with respect to SDADC output data rate. Refer to chapter Configurations for more details. Parameters *ato\_p\_gain* and *ato\_i\_gain* are constants of ATO PI controller, refer to *Resolver ATO PI-gains.xlsx* for the particular configurations. Excitation signal phase shift adjustment is controlled by PI controller with parameters *exc\_p\_gain* and *exc\_i\_gain* that are configured empirically. The configuration used in this example is

recommended. Last parameter *q\_ewma\_speed* is an EWMA filter coefficient used to filter ATO speed updates. Is should be ~0.9 meaning the 0.9 weight is applied on previous filtered speed value.

```

struct resolver config t resolver config =

ł

FS ETPU RESOLVER SEMAPHORE 0, /* smpr id */

FS ETPU RESOLVER OPTIONS CALCULATION ON +

FS ETPU RESOLVER OPTIONS DIAG MEASURES ON +

FS ETPU RESOLVER OPTIONS DIAG FLAGS ON +

FS ETPU RESOLVER OPTIONS EXC ADAPTATION ON +

FS ETPU RESOLVER OPTIONS EXC GENERATION ON+

FS ETPU RESOLVER OPTIONS RDC CHECKER ON, /* options */

NSEC2TCR1(99840), /* excitation period */

SFRACT24(0.070597541), /* ato p gain */

SFRACT24(0.002492006), /* ato i gain */

SFRACT24(0.00000), /* exc p gain */

SFRACT24(0.00012), /* exc i gain */

SFRACT24(0.99) /* q ewma speed */

};

```

Define Resolver Diag thresholds structure: This is used when diagnostics running on eTPU are enabled. This structure contains thresholds that are compared against the diagnostic measures and diagnostic flags are set upon that comparison. For detailed description of each threshold and diagnostic measures please refer to chapter eTPU diagnostics.

```

struct resolver_diag_thresholds_t resolver_diag_thresholds =

{

SFRACT24(0.6), /* ampl_thrs */

SFRACT24(0.15), /* low_ampl_thrs */

SFRACT24(0.05), /* mean_thrs */

SFRACT24(0.4*0.4), /* vec_min_thrs */

SFRACT24(0.6*0.6), /* vec_max_thrs */

SFRACT24(0.1), /* ampl_diff_thrs */

SFRACT24(0.1), /* ampl_diff_thrs */

SFRACT24(5.0/360), /* ato_angle_err_thrs */

RPM2FRACT(10000, 99840) /* ato_speed_max_thrs */

};

```

• Define rest of the structures containing ATO and diagnostics and states.

```

struct resolver_outputs_t resolver_outputs_calculated;

struct resolver_outputs_t resolver_outputs_extrapolated;

struct resolver_outputs_t resolver_outputs_mechanical;

struct resolver_diag_measures_t resolver_diag_measures;

struct resolver_diag_flags_t resolver_diag_flags;

struct resolver_states_t resolver_states;

```

Implement the eTPU initialization – modify my\_system\_etpu\_init() function with adding Resolver initialization from Resolver API. This function call comes after global eTPU initialization as follows.

```

/* Initialization of eTPU channel settings */

err_code = fs_etpu_resolver_init(&resolver_instance, &resolver_config);

if(err code != FS ETPU ERROR NONE) return(err code + (ETPU RESOLVER EXC CHAN<<16));</pre>

```

Call the my\_system\_etpu\_init() and my\_system\_etpu\_start() in main function to get the configuration done and start eTPU. Note that also for proper Resolver operation it requires to configure and start DMA and SDADC as well. See the correct sequence of calling the routines below.

```

/* initialize eTPU */

my system etpu init();

```

```

/* Initialize eDMA */

edma_init();

/* SDADC init*/

sdadc_init();

/* run the eTPU */

my_system_etpu_start();

/* start the DMA */

edma_start();

/* start the SDADC */

sdadc_start();

```

Use the functions from Resolver API (etpu\_resolver.c/.h) to interface Resolver function in runtime.

## 2.2 How to include RDC Checker into application

To correctly run the RDC Checker user has to get the Resolver function up and running (as described in previous chapter How to get eTPU Resolver function up and running within CPU application) at first. Then you have to include rdc\_checker.c/.h files into the project and perform threshold configuration. Also DMA has to be configured to transfer data upon ATO Resolver eTPU channel request. All the necessary steps are further described in detail.

- Include RDC Checker files. The files should be included into the main.c.

- Configure DMA: The configuration of particular DMA channel that is triggered by eTPU ATO channel has to be performed to transfer data from eTPU data RAM into *Rdc\_InputData* structure that is defined as a global variable within the *rdc\_checker.c* file. For more details please refer to chapter DMA configuration for RDC Checker.

- Modify the RDC Checker thresholds that are defined in *rdc\_checker.h* and can be modified by user according to

application needs. The thresholds are equivalent to resolver diagnostic thresholds

```

/* RDC Checker fault thresholds */

#define RDC_THR_SIG_MAX_AMPL RDC_FRACT16(0.8)

#define RDC_THR_SIG_DC_SHFT RDC_FRACT16(0.05)

#define RDC_THR_SIG_ZC_AMPL RDC_FRACT16(0.05)

#define RDC_THR_VEC_MIN_SQR RDC_FRACT16(0.6 * 0.6)

#define RDC_THR_ATO_ERR RDC_FRACT16(0.8 * 0.8)

#define RDC_THR_EXT RDC_FRACT24(2.0/360.0)

#define RDC_THR_TIMING (1997)

#define RDC_PERIOD TCR1 (19968)

```

## 2.3 How to run RDC checker within application

There are two options how to use the RDC Checker within the application:

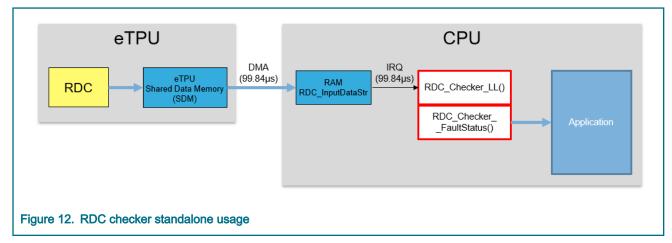

Stand-alone checker: After RDC\_Checker\_LL() call RDC\_Checker\_FaultStatus() to get all detected fault flags and process

them using accumulation, delay, decoupling and other techniques. The following figure shows the timing diagram.

The example can be found within the testing application *MPC5777C\_RDC\_Checker* attached to this document where the interrupt routine on DMA channel transfer completion is used to run the RDC Checker.

```

void DMA Isr(void)

{

/* low level RDC Checker performs input data check and ^{\ast/}

RDC Checker LL();

/\,\star\, Read the fault status from LL RDC checker \,\star/\,

RDC fault = RDC Checker FaultStatus();

if( RDC fault == 0)

{

/* no fault - normal operation */

}

else

{

if(first_fault) /* First fault state detected - capture the transient fault */

{

first fault = RDC fault;

}

else

{

accumulated_faults |= RDC_fault;

fault_cnt++;

if(fault cnt > 100)

{

/* Report to Safety manager */

RDC Checker();

/* Clear counters and fault variables */

fault cnt = 0;

first fault = 0;

accumulated faults = 0;

}

}

}

/* Clear the interrupt flag */

DMA A.CINT.B.CINT = 28;

}

```

• RDC Checker used within the SRF: *RDC\_Checker\_LL()* runs on DMA interrupt request. The *RDC\_Checker()* runs periodically as one of the 100µsec tasks and reports to SRF Safety Manager (see the following figure). The Safety Manager handles the reported faults, their decoupling and execution of safety reaction.

# Chapter 3 Configurations

# 3.1 DMA configuration for RDC checker

Configuration of DMA channel that is triggered by Resolver ATO channel to transfer data from eTPU memory (resolver\_instance. checker\_signals\_pba) to *Rdc\_InputData* structure that is used by RDC Checker is described in the folloing table.

| Table 13. | DMA | configuration | for <b>R</b> | <b>RDC checker</b> |

|-----------|-----|---------------|--------------|--------------------|

|-----------|-----|---------------|--------------|--------------------|

| Configuration Item                  | RDC Checker DMA channel                                                           |

|-------------------------------------|-----------------------------------------------------------------------------------|

| Source address                      | resolver_instance.checker_signals_pba+ 0x4000<br>(reading from PSE memory region) |

| Destination address                 | &Rdc_InputData.sin08<br>(first member of <i>Rdc_InputData</i> structure)          |

| Source transfer size / modulo       | 32-bits / 0 bytes                                                                 |

| Destination transfer size / modulo  | 32-bits / 44 bytes                                                                |

| Source address offset               | 4 bytes                                                                           |

| Destination address offset          | 4 bytes                                                                           |

| Minor loop byte count               | 44 bytes                                                                          |

| Major loop iteration count          | 1                                                                                 |

| Last source address adjustment      | -44 bytes                                                                         |

| Last destination address adjustment | -44 bytes                                                                         |

| Channel to channel linking          | disabled                                                                          |

| Linked channel                      | -                                                                                 |

| Interrupt on major loop complete    | enabled                                                                           |

# 3.2 SDADC config

Reffer to the description in chapter Sine and Cosine feedack signal digitization for the reference.

## 3.3 ADC delay parameter

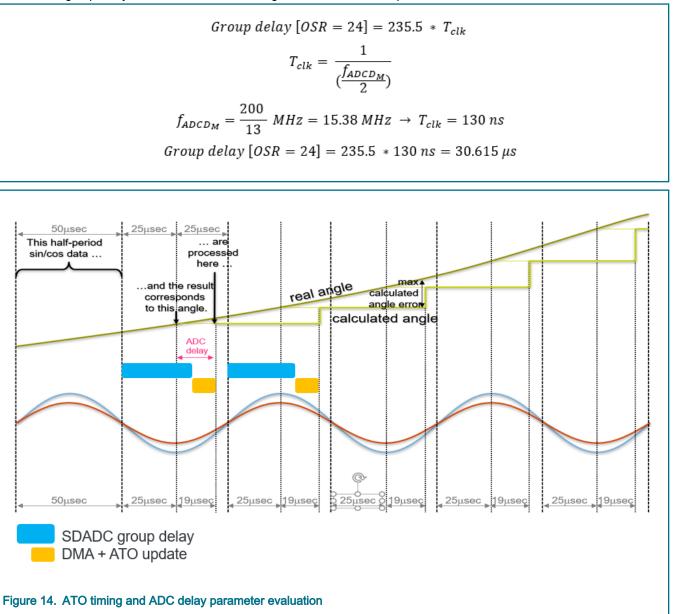

The parameter *adc\_delay* is evaluated based on SDADC group delay as well as ATO updated calculation time together with delay caused by transferring the samples from SDADC result FIFO into eTPU data memory using DMA. Another important information taken into account is that angle value calculated from sin/cos half-period N, corresponds to the time position of the next, N+1<sup>st</sup>, half-period center, because the ATO output is actually prediction of the angle for next half-period. The ADC delay is then evaluated as time difference between the ATO N end of update and the center of N+1 half-period. The evaluation is described in ATO timing and ADC delay parameter evaluation.

The SDADC group delay can be evaluated according to SDADC electrical specifications as follows.

## 3.4 Start offset configuration

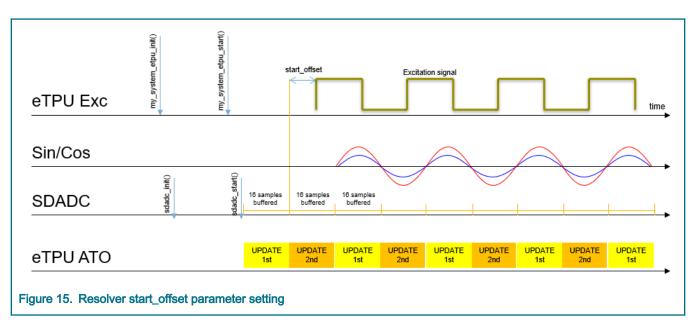

*Start\_offset* parameter determines the time when the generation of excitation signal starts after first ATO 1<sup>st</sup> host service request is received. It is important to evaluate this parameter since RDC function generates excitation signal as a PWM signal with 50 % duty cycle. This is then supposed to be fed into analog filters and further to resolver sensor excitation input. This HW chain causes a certain phase shift which is propagated into sine and cosine feedback signals. For the eTPU RDC it is crutial to have the feedback signals aligned in the buffers so the first-half period of the buffer contains the part of the signal corresponding to first half-period of excitation signal. At the eTPU RDC function startup the excitation signal phase shift is adjusted so the feedback signals are aligned in the signal buffers and zero-crossing error is minimized. The *start\_offset* parameter has to be handled carefully to prevent locking the feedback signals into buffers with 180 degree error. The start\_offset parameter and its relation to the excitation signal and feedback signals is illustrated in the following figure.

# Chapter 4 APIs

## 4.1 eTPU Resolver API

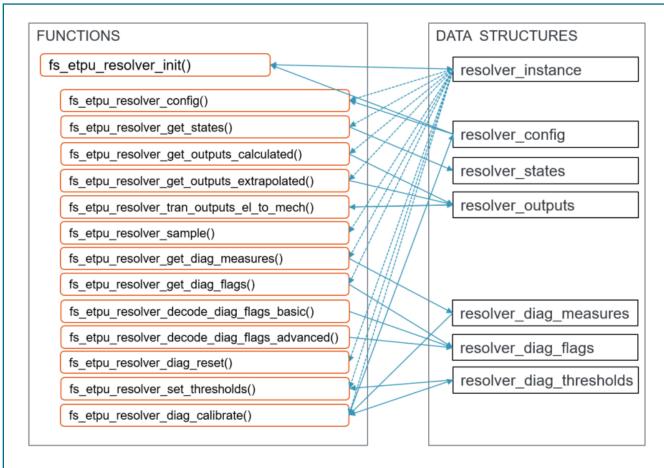

The Resolver Digital Interface API is used to control and monitor the eTPU function using the following routines:

- fs\_etpu\_resolver\_init()

- fs\_etpu\_resolver\_config()

- fs\_etpu\_resolver\_get\_states()

- fs\_etpu\_resolver\_get\_outputs\_calculated()

- fs\_etpu\_resolver\_get\_outputs\_extrapolated()

- fs\_etpu\_resolver\_trans\_outputs\_el\_to\_mech()

- fs\_etpu\_resolver\_sample()

- fs\_etpu\_resolver\_get\_diag\_measures()

- fs\_etpu\_resolver\_get\_diag\_flags()

- fs\_etpu\_resolver\_decode\_diag\_flags\_basic()

- fs\_etpu\_resolver\_decode\_diag\_flags\_advanced()

- fs\_etpu\_resolver\_diag\_reset()

- fs\_etpu\_resolver\_set\_thresholds()

- fs\_etpu\_resolver\_diag\_calibrate()

These API functions handle the following data structures:

- resolver\_instance

- resolver\_config

- · resolver\_outputs

- resolver\_diag\_measures

- · resolver\_diag\_thresholds

- resolver\_diag\_flags

- resolver\_states

The data structures include the following fields:

#### NOTE

For a detailed API description refer to RESOLVER-DoxyDoc.chm or RESOLVER-DoxyDoc.zip which are included in AN5335SW.

Interaction among the API routines and data structures is shown in the following figure.

#### Figure 16. Resolver API functions and data structures

## 4.2 RDC Checker API

The RDC Checker API includes the following routines:

```

void Rdc_Checker_LL( void )

uint32_t Rdc_Checker_FaultStatus( void )

void Rdc_Checker( void )

uint32_t Rdc_FaultInj( void )

```

- Rdc\_Checker\_LL is the low-level checker routine which, on DMA IRQ, checks the eTPU data and set fault flags

- *Rdc\_Checker\_FaultStatus* returns the detected fault flags and cleans them. The fault flags are cumulated until cleaned by *Rdc\_Checker\_FaultStatus* or *Rdc\_Checker*.

- Rdc\_Checker is intended to report cumulated flags to SRF Safety Manager and clean them.

- Rdc\_FaultInj is intended to be used within the SRF as part of a self-check by fault injection.

The RDC Checker detects the following fault flags (fault status).

```

/* RDC Checker fault flags */

#define RDC_FAULT_SIN_STUCK (0x0001UL)

#define RDC_FAULT_COS_STUCK (0x0002UL)

#define RDC_FAULT_SIN_AMPL_OOR (0x0004UL)

#define RDC_FAULT_COS_AMPL_OOR (0x0008UL)

#define RDC_FAULT_SIN_DC_SHFT (0x0010UL)

#define RDC FAULT COS DC SHFT (0x0020UL)

```

APIs

# Chapter 5 Demos and Application Notes

## 5.1 RDC Checker testing application

The RDC Checker testing application *MPC5777C\_RDC\_Checker* is showing the use of Resolver function together with RDC Checker in stand-alone option. Note that in this application no real Resolver HW is used, the feedback signals are emulated within the PIT Timer interrupt routine and placed into eTPU data RAM on signal\_pba address. Also the DMA together with SDADCs are not used here, HSR request are written into the Resolver ATO channel at the end of PIT Timer ISR by using Resolver API function. Within this application several test-cases are defined to demonstrate the RDC Checker functionality.

# Chapter 6 References

### Table 14. References

| S. No. | Description                          | Location    |

|--------|--------------------------------------|-------------|

| 1.     | SRF_PIM_MPC5775E_BETA_0.9.0          | www.nxp.com |

|        | (January 2019)                       |             |

|        | Includes SRF, RDC Checker, and more. |             |

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/ SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, UMEMS, EdgeScale, EdgeLock, elQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2020.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: March 2020 Document identifier: eTPURDCCUG