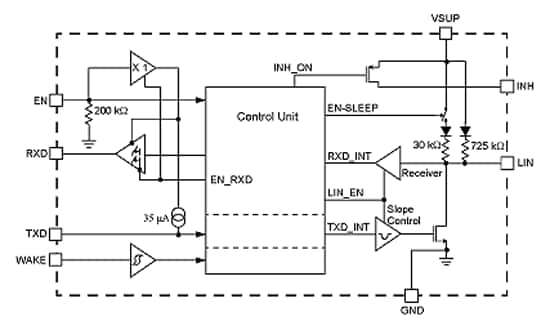

The NXP® MC33662 is a physical layer component dedicated to automotive LIN sub-bus applications.

- Designed to support automotive networks with Controller Area Network (CAN)

- Part number selection defines the operating baud rate (33662L or 33662S for 20 kB/s and 33662J for 10 kB/s)

- Both integrate a fast baud rate (100 kB/s) for test and programming modes

- Provides excellent Electromagnetic Compatibility (EMC) and Radiated Emission performance, Electrostatic Discharge (ESD) robustness and safe behaviour in case of TXD short to ground

評価・開発ボード

評価・開発ボード 完全なソリューション

完全なソリューション 完全なソリューション

完全なソリューション