デザイン・ファイル

2 設計・ファイル

-

シミュレーションとモデル

BSDL for LPC18xx and LPC43xx

-

シンボルおよびフットプリント

LPC43xx/LPC18xx Eagle symbols

お客様の素早い設計とより早い製品化を実現する、技術情報と専門知識をご紹介します。

The LPC18S37JET100 is a Arm Cortex-M3 based microcontroller for embedded applications. The Arm Cortex-M3 is a next generation core that offers system enhancements such as low power consumption, enhanced debug features, and a high level of support block integration.

The LPC18S37JET100 operates at CPU frequencies of up to 180 MHz. The Arm Cortex-M3 CPU incorporates a 3-stage pipeline and uses a Harvard architecture with separate local instruction and data buses as well as a third bus for peripherals. The Arm Cortex-M3 CPU also includes an internal prefetch unit that supports speculative branching.

The LPC18S37JET100 includes 1 MB of flash and 136 kB of on-chip SRAM, 16 kB of EEPROM memory, a quad SPI Flash Interface (SPIFI), a State-configurable Timer/PWM (SCTimer/PWM) subsystem, two High-speed USB controllers, Ethernet, an external memory controller, and multiple digital and analog peripherals.

部品番号: LPC18S37JET100.

クイック・リファレンス ドキュメンテーションの種類.

1-5 の 13 ドキュメント

セキュアファイルの読み込み中、しばらくお待ちください。

2 設計・ファイル

セキュアファイルの読み込み中、しばらくお待ちください。

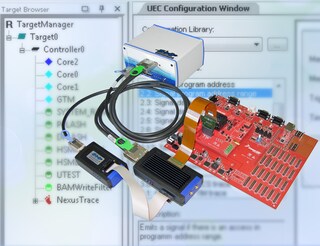

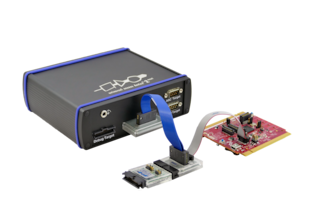

1-5 の 7 ハードウェア提供

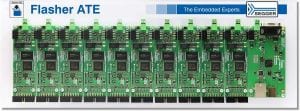

追加ハードウェアを利用可能 パートナー・ソリューションの特集を表示.

1-5 の 9 ハードウェア提供

本製品をサポートするパートナーの一覧は、 パートナーマーケットプレイス.

1-5 の 6 ソフトウェア・ファイル

追加ソフトウェアを利用可能 パートナー・ソリューションの特集を表示.

注: より快適にご利用いただくために、ソフトウェアのダウンロードはデスクトップで行うことを推奨します。

セキュアファイルの読み込み中、しばらくお待ちください。

1-5 の 47 ソフトウェア提供

本製品をサポートするパートナーの一覧は、 パートナーマーケットプレイス.

1-5 の 6 エンジニアリング・サービス

There are no results for this selection.

本製品をサポートするパートナーの一覧は、 パートナーマーケットプレイス.

6 トレーニング

6 トレーニング