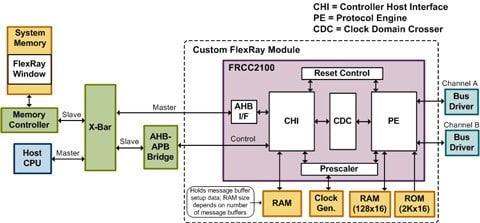

The FRCC2100 fully complies with FlexRay Communication System Protocol Specification, Version 2.1, Revision A. It implements the specification-defined Controller Host Interface (CHI) and Protocol Engine (PE) functionality, with clean partitioning between the CHI and PE functional blocks.

The FRCC2100 supports 4–252 message buffers and features standard interfaces to system logic and memories, so it can be readily optimized to your system requirements and easily integrated into your FPGA or ASIC device.

The host CPU interface is similar to the AMBA 2 APB. Example glue logic to connect to AMBA 2 APB is included with the product. The interface to FlexRay memory, which stores the message buffer header, payload, and status, is AMBA 2 AHB and can be adapted to other system memory interfaces upon request.

A rich ecosystem, including support from leading FlexRay software providers and a starter kit available for evaluation and prototyping, enables rapid software development.