Getting Started with the S32G Reference Design Board 3 for Vehicle Network Processing

Contents of this document

-

Out of the Box

-

Get Software

-

Plug It In

-

Run

Sign in to save your progress. Don't have an account? Create one.

Purchase your S32G3 Vehicle Networking Reference Design

1. Out of the Box

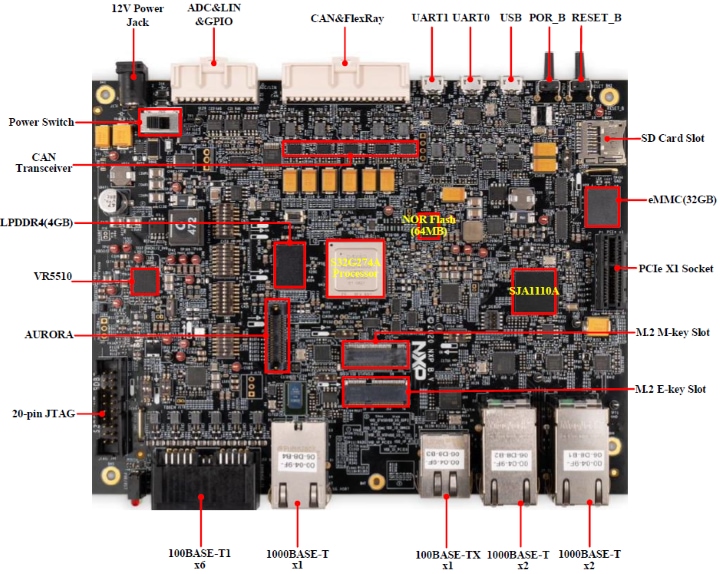

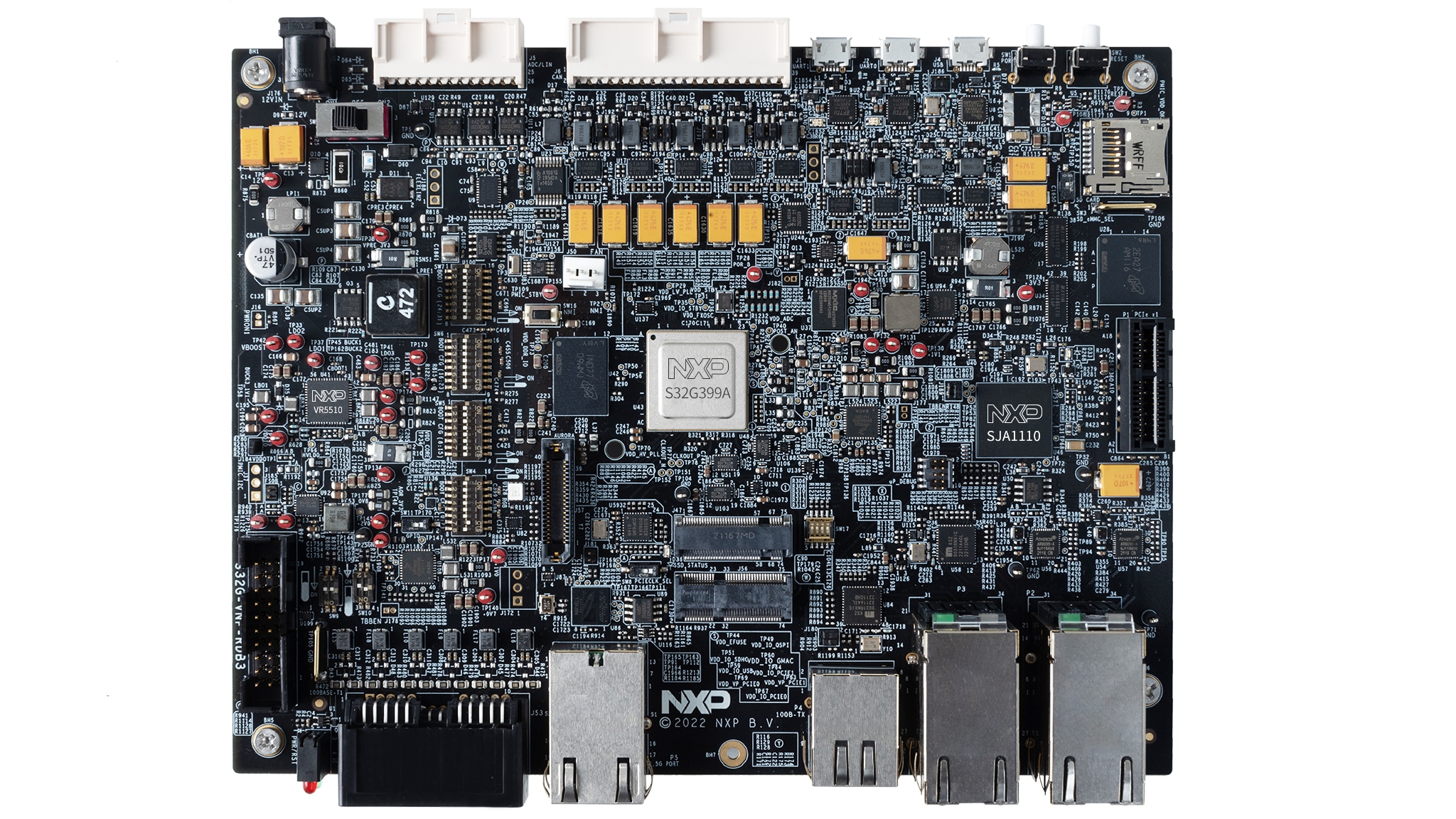

1.1 Get to Know the S32-VNP-RDB3 Reference Design Board for Vehicle Network Processin

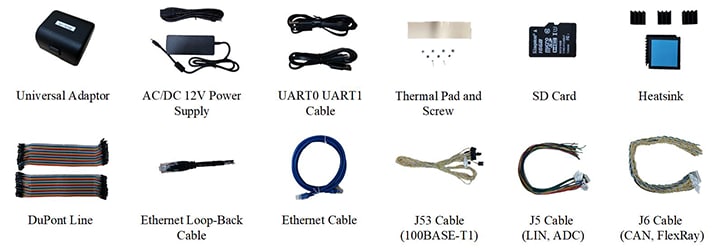

1.2 Get to Know the Complete Board Kit

2. Get Software

Learn how to use the Automotive Software Package Manager

2.1 Install a Terminal Emulator for Console

Install any Terminal Emulator familiar to you, such as Tera Term, Putty and other.

We recommend to use the Tera Term 2.3. Tera Term is open source free software terminal emulator supporting UTF-8 protocol. Now TTSSH supports SSH2 protocol (original version supports SSH1).

2.2 Install FTDI CDM WHQL Driver

FTDI CDM v2.12.28 WHQL driver for serial configuration from FTDI chip.

3. Plug It In

Let’s take your S32-VNP-RDB3 board for a test drive.

3.1 Plug in the SD card

The SD card has pre-loaded Linux BSP image in the factory, you just need to plug SD card into the respective slot in your S32G-VNP-RDB3 board.

3.2 Plug in the UART cable

Use the Micro-AB interface of the UART cable to connect the

S32G-VNP-RDB3’s UART0 port.

Use the typeA interface of the UART cable to connect to the PC.

3.3 Plug in the 12 V Power Supply

Connect the power supply to the 12 V power jack on S32G-VNP-RDB3.

4. Run

4.1 Setup Console

- Open your Terminal Emulator for Console.

- Select the serial port to which can be found in "Device Manager" of the PC and click OK

-

Go to Setup → Serial Port and select

115200as the baud rate

4.2 Power the Board On

Toggle the power switch SW15 to the left side of your S32G-VNP-RDB3 board.

The left side is the viewing angle of the picture in Chapter 1.1

4.3 Run Linux BSP

The Linux BSP is automatically executed from the SD card.

The console display on Tera Term shows the running logs of Linux BSP.

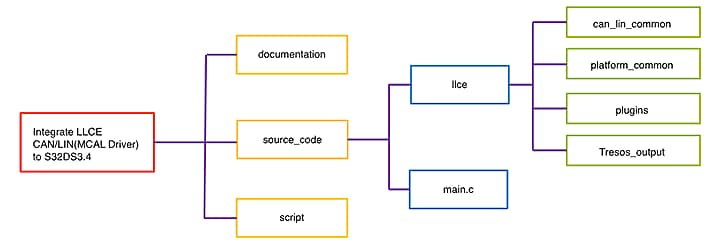

Integrate LLCE CAN/LIN MCAL Driver

High-level Code Structures

Providing an easy way to integrate Low Latency Communication Engine (LLCE) CAN/LIN MCAL driver into S32DS as LLCE 1.0.0 driver does not integrate to S32DS 3.4 environment.

The software package structure:

Hardware and Software Requirements

| Host PC with Windows OS with serial console | ||

|---|---|---|

| S32G-VNP-RDB3 REV C/D |

- |

|

| LLCE demo code | ||

| Real-Time Drivers (RTD) 1.0.0 | ||

| Low Latency Communication Engine (LLCE) 1.0.0 | ||

| S32 Design Studio for S32 Platform (Building LLCE project) | ||

| S32 Design Studio for S32 Platform (MCAL configuration for LLCE) | ||

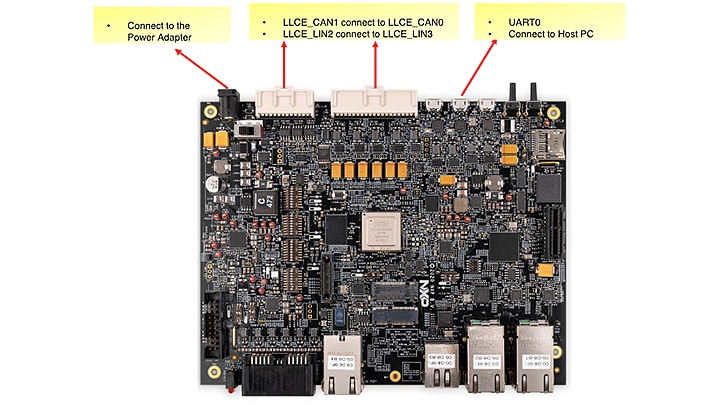

S32G-VNP-RDB3 Connection

Plug LLCE CAN/LIN and UART0 connectors, also power your S32G-VNP-RDB3.

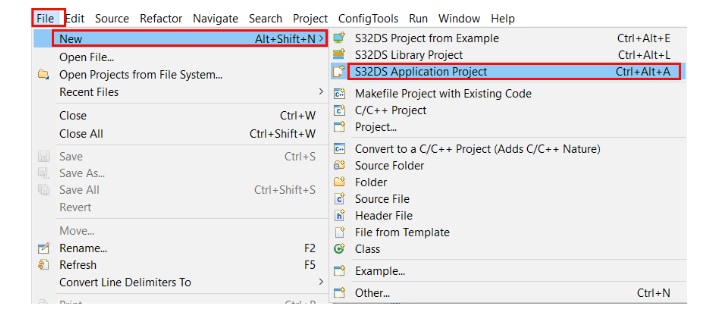

Create a New Project in S32DS

Launch S32 Design Studio for S32 platform , then follow File → New S32DS Application Project:

Choose S32G274A_Rev2_Cortex-M7 from Project name and then click Next

Only choose Cortex-M7_0, select SDKs as RTD1.0.0 and then click Finish

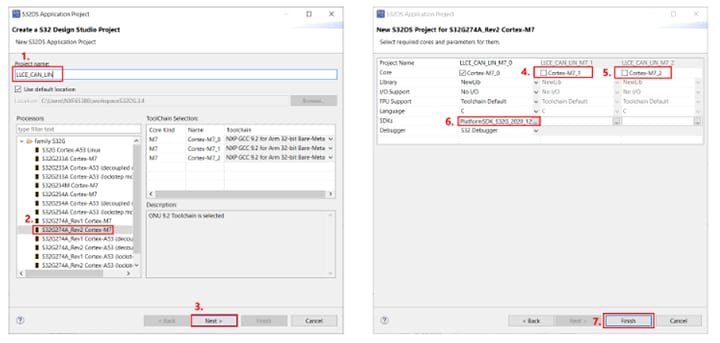

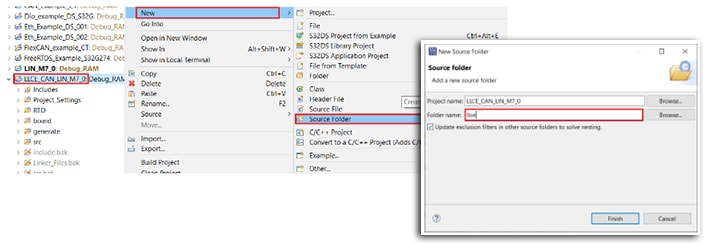

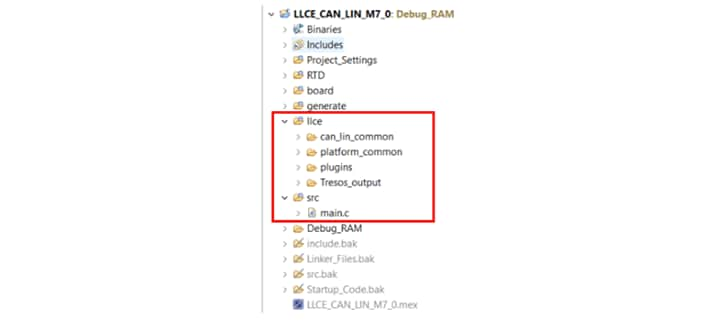

Right click the project, New → Source Folder and create a Folder named

llce

Copy the LLCE CAN/LIN related source code to llce folder and replace the main.c to integrate LLCE CAN/LIN related source code to project.

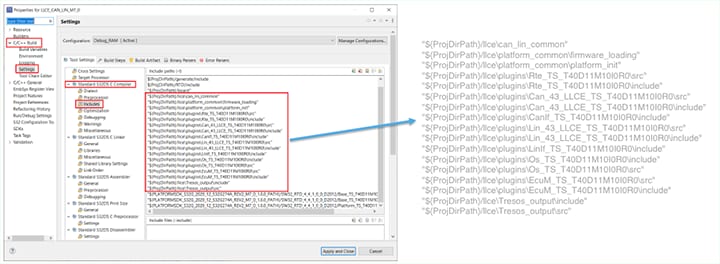

Right click the project and go through Properties → C/C++ Build → Settings → Standard S32DS C Compiler → Include to add the path:

"${ProjDirPath}/llce\can_lin_common"

"${ProjDirPath}/llce\platform_common\firmware_loading"

"${ProjDirPath}/llce\platform_common\platform_init"

"${ProjDirPath}/llce\plugins\Rte_TS_T40D11M10I0R0\src"

"${ProjDirPath}/llce\plugins\Rte_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\plugins\Can_43_LLCE_TS_T40D11M10I0R0\src"

"${ProjDirPath}/llce\plugins\Can_43_LLCE_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\plugins\CanIf_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\plugins\Lin_43_LLCE_TS_T40D11M10I0R0\src"

"${ProjDirPath}/llce\plugins\Lin_43_LLCE_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\plugins\LinIf_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\plugins\Os_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\plugins\Os_TS_T40D11M10I0R0\src"

"${ProjDirPath}/llce\plugins\EcuM_TS_T40D11M10I0R0\src"

"${ProjDirPath}/llce\plugins\EcuM_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\Tresos_output\include"

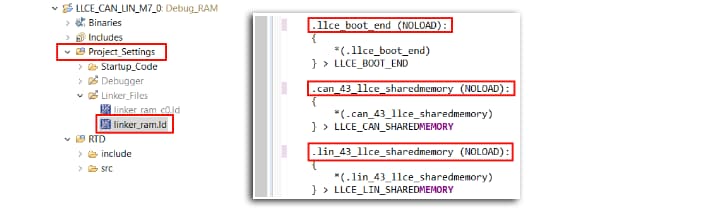

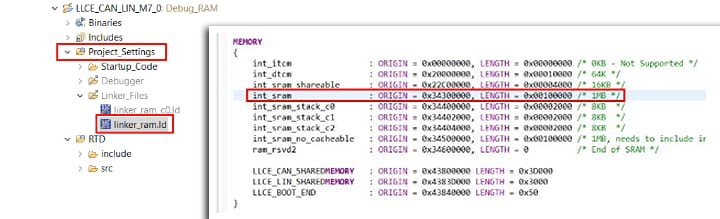

"${ProjDirPath}/llce\Tresos_output\src"Follow the path: Project_Settings → Linker_Files → linker_ram.ld

- Add

(NOLOAD)behind the.llce_boot_end,.can_43_llce_sharedmemory, and.lin_43_llce_sharedmemory

- Also, modify

init_srammemory node as follows:

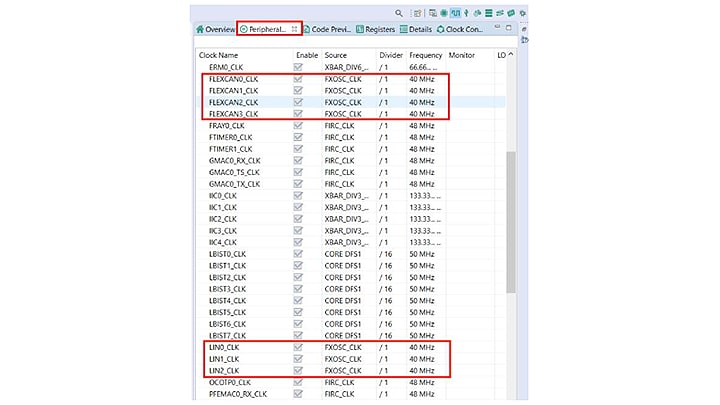

Open ConfigTools → Clocks for setting llce_can/lin clock as

40 MHz

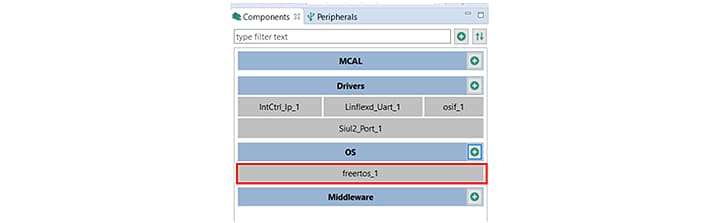

Open ConfigTools → Peripherals, add the freertos from the OS component:

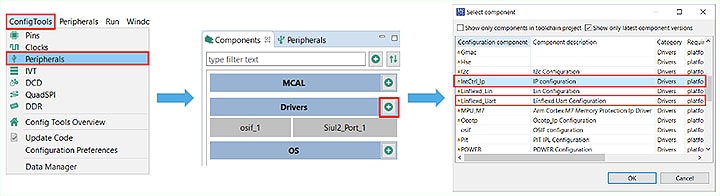

Open ConfigTools → Peripherals, add IntCtrl_Ip and Linflexd_Uart driver from the Drivers component:

Double click IntCtrl_Ip and add a new Interrupt Controller to enable LINFLED0_IRQn

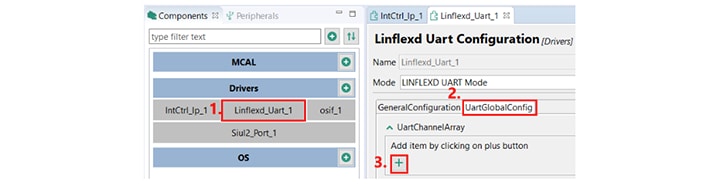

Double click Linfled_Uart_1 and add a new UartGlobalConfig with default settings.

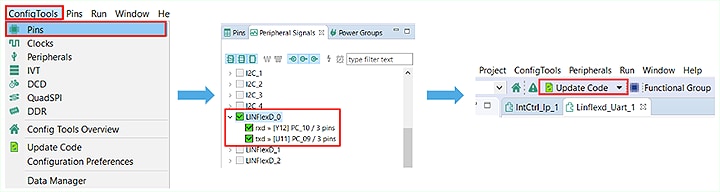

Open ConfigTools → Pins to set up the LINFlexD_0's pins (PC_09 and PC_10) and then click Update code

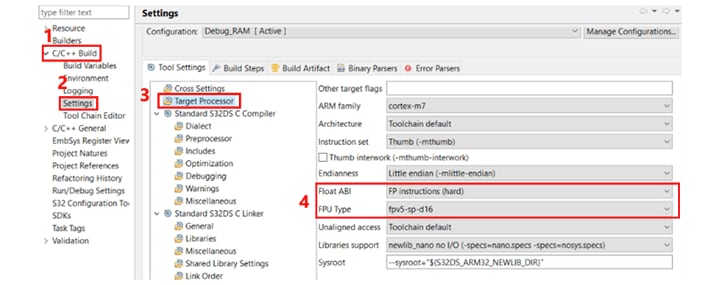

Right click the project, then follow Properties → C/C++ Build → Settings → Target Processor Select Float ABI as FP instructions (hard):

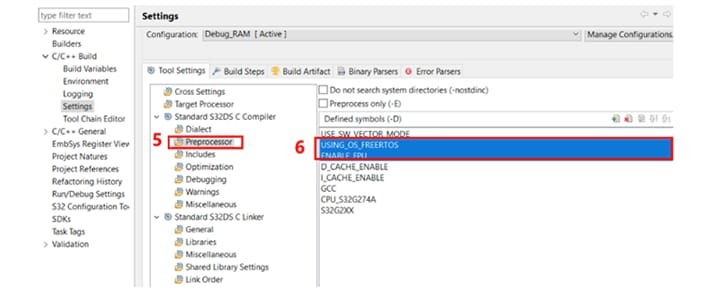

Right click the project, then follow Properties → C/C++ Build → Settings → Preprocessor Add USING_OS_FREERTOS and ENABLE_FPU

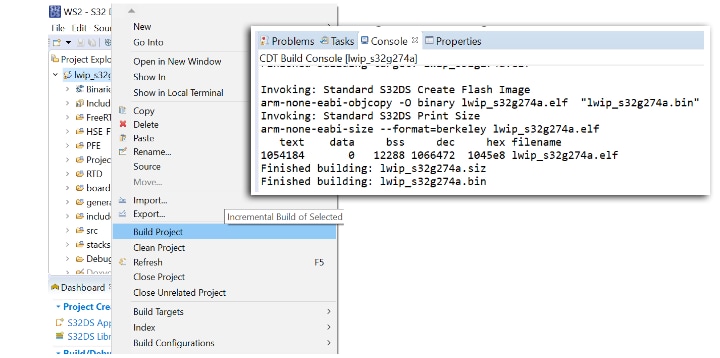

Build the project, the LLCE_CAN_LIN_M7_0.elf will be generated Convert the LLCE_CAN_LIN_M7_0.elf to LLCE_CAN_LIN_M7_0.bin:

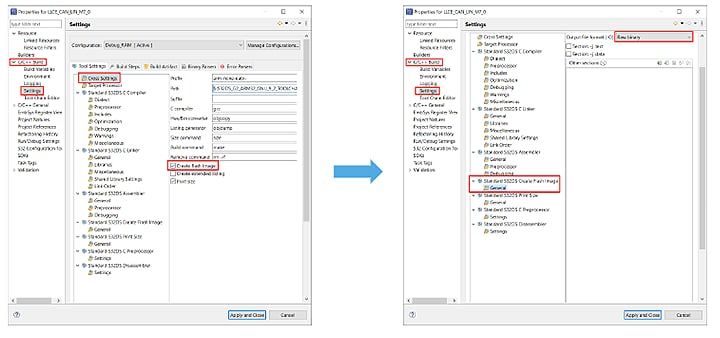

- Right click project file and open Properties → C/C++ Build → Settings → Cross Settings Enable the Create flash Image option and then click Apply and Close

- Right click project file again and open Properties → C/C++ Build → Settings → Standard S32DS Create Flash Image. Change Output file format as

Raw binaryand then click Apply and Close - Rebuild the project

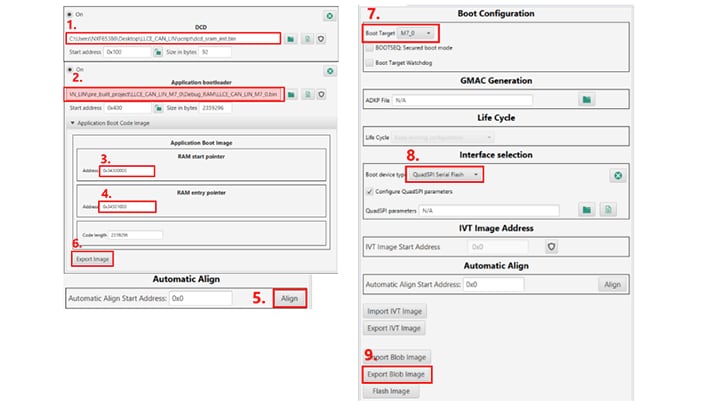

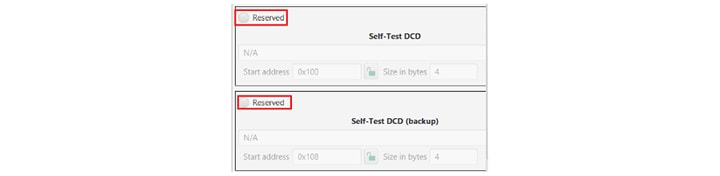

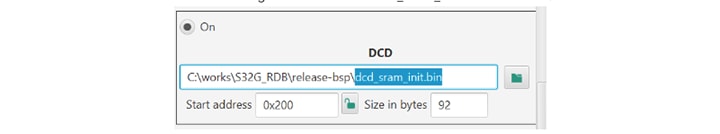

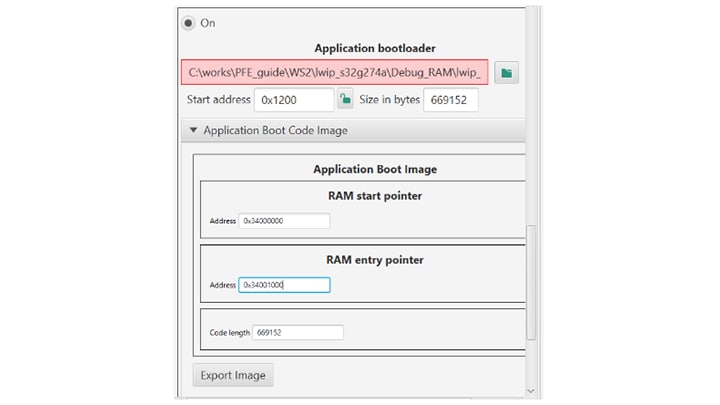

Generate LLCE_CAN_LIN_M7_0_IVT.bin based on the S32DS 3.4 IVT tools:

- Select DCD and add the script directory

- Select Application bootloader and add the directory

- Fill the RAM start pointer, the RAM entry pointer and the Codelength

- Click Align button

- Click Export Image and save the “blob” binary

- Select Boot Target to be

M7_0 - Select Boot device type to be

QuadSPI Serial Flash -

Click on Export Blob Image and save the binary as

LLCE_CAN_LIN_M7_0_IVT.bin

LCCE CAN/LIN test

Set your S32G-VNP-RDB3 to serial boot mode by turning both SW9 [0:1] and SW10 [0:1] to OFF:OFF

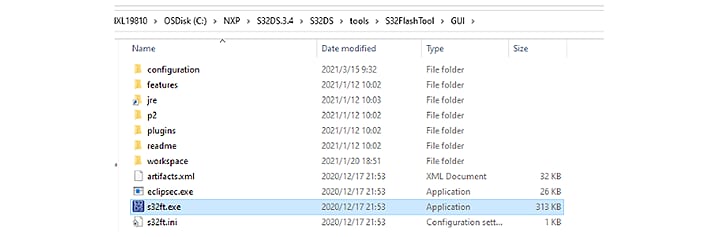

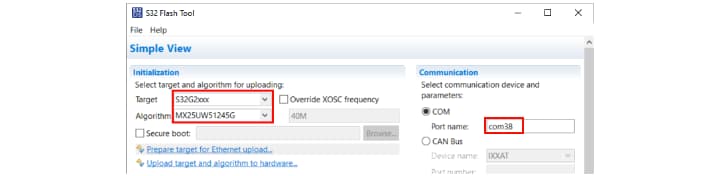

Power the board on, and open the s32ft.exe flash tool under the S32DS 3.4 installation folder:

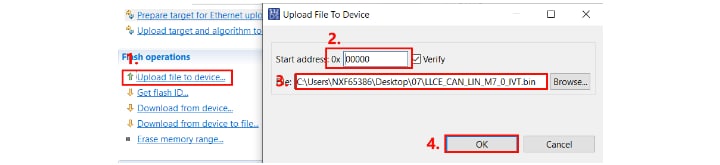

Upload the LLCE_CAN_LIN_M7_0_IVT.bin into the QSPI NOR Flash by using Flash tool.

Target : S32Gxxx. Algorithm: MX25UW51245G.

COM: Please check the com number on the HOST PC for UART0.

Click Upload target and algorithm to hardware to initialize the hardware. Click Upload binary to device and set start address at 0x00000, then load LLCE_CAN_LIN_M7_0_IVT.bin into QSPI and click OK.

Set your S32G-VNPRDB2 to QSPI boot mode by turning SW9 [0:1] to OFF:OFF and SW10 [0:1] to ON:OFF (for BOOT from RCON) plus SW4 [6:8] to OFF:OFF:OFF (to boot from QSPI Flash).

Connect LLCE CAN0 to LLCE CAN1 and connect LLCE LIN2 (leader) to LLCE LIN3 (follower).

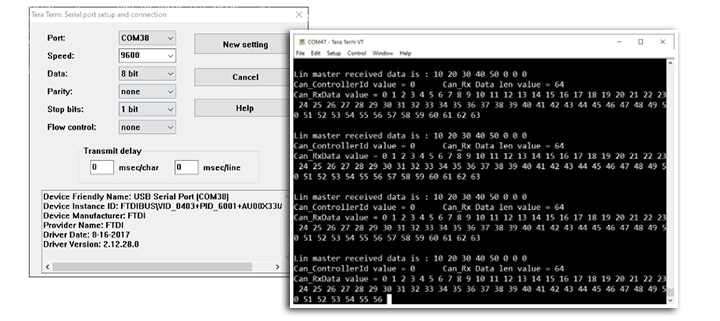

Open serial console (e.g: Tera Term) for UART0 on Host PC, set bitrate as 9600. Power on the board and wait for console printings:

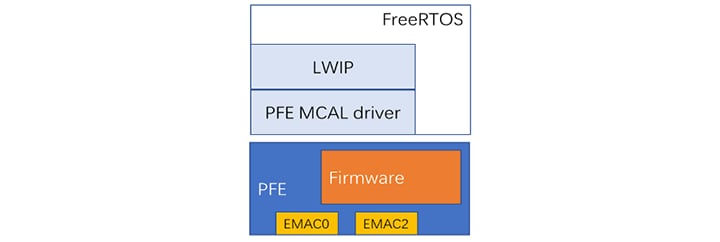

Enable PFE Ethernet interface with lwIP and FreeRTOS on the S32G-VNP-RDB3's S32G274A Arm® Cortex®-M7 core

An example project that enable Packet Forwarding Engine (PFE) Ethernet interface with a lwIP (lightweight IP) stack and FreeRTOS on the S32G's M7 core. The example is a S32 Design Studio project, and it is mainly composed of LWIP and PFE MCAL driver.

Hardware and Software Requirements

| Host PC with Windows OS with serial console | ||

|---|---|---|

| S32G-VNP-RDB3 REV C/D |

- |

|

| PFE demo code | ||

Enabling PFE Ethernet Interface

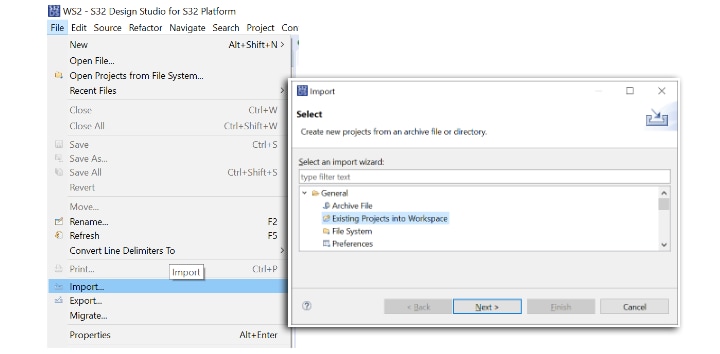

Launch S32 Design Studio for S32 platform and import the example project using the Existing Projects into Workspace option:

Once loaded, click the Build Project option. Get the results once the built is complete:

Make and IVT image by selecting the dcd_sram_init.bin DCD file for clearing

SRAM.

Set RAM start pointer as 0x34000000 and RAM entry pointer as

0x34001000 for application boot image.

Then write a final blob image to the SD card for testing.

Linux BSP Running Logs

Linux BSP Running Logs

U-Boot 2019.04+ga53a9fa1e9 (Aug 31 2020 - 05:07:39 +0000)

CPU: NXP S32G274A rev. 2.1.0

Reset cause: Power-On Reset

Model: NXP S32G27x

Board: NXP S32G274A-RDB

DRAM: 512 MiB

CA53 core 1 running.

CA53 core 2 running.

CA53 core 3 running.

All (4) cores are up.

MMC: FSL_SDHC: 0

Loading Environment from MMC... OK

Using external clock for PCIe0

Configuring PCIe0 as RootComplex(x2)

Using external clock for PCIe1

Frequency 125Mhz configured for PCIe1

Configuring PCIe1 as SGMII(x2) [XPCS0 2.5G, XPCS1 OFF]

PCIe0: Failed to get link up

Pcie0: LINK_DBG_1: 0x00000000, LINK_DBG_2: 0x00000800 (expected 0x000000d1)

DEBUG_R0: 0x0052a300, DEBUG_R1: 0x08200000

PCIe1: Not configuring PCIe, PHY not configured

In: serial

Out: serial

Err: serial

Net: EQOS phy: rgmii fixed-link

Warning: eth_eqos (eth0) using random MAC address - 8a:54:02:e5:1f:1a

eth0: eth_eqos PFE: emac0: sgmii emac1: none emac2: rgmii

Warning: eth_pfeng using MAC address from ROM

, eth1: eth_pfeng

Hit any key to stop autoboot: 0

PFE: emac0: sgmii emac1: none emac2: rgmii

PFE: emac0: sgmii emac1: none emac2: rgmii

switch to partitions #0, OK

mmc0 is current device

9158664 bytes read in 400 ms (21.8 MiB/s)

Booting from mmc ...

9158664 bytes read in 385 ms (22.7 MiB/s)

27786 bytes read in 7 ms (3.8 MiB/s)

## Flattened Device Tree blob at 83e00000

Booting using the fdt blob at 0x83e00000

Loading Device Tree to 000000009fafa000, end 000000009fb03c89 ... OK

Reserving 2048k off the top of [c0000000-dfffffff] for protected RAM

DT: Enabling PFE

DT: Enabling PFE_EMAC_0

DT: pfe0 set to 00:01:be:be:ef:11

DT: Disabling PFE_EMAC_1

DT: Enabling PFE_EMAC_2

DT: pfe2 set to 00:01:be:be:ef:33

DT: Enabling GMAC

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0000000000 [0x410fd034]

[ 0.000000] Linux version 4.19.59-rt24+ged566620fe59 (oe-user@oe-host) (gcc version 9.2.0 (GCC)) #1 SMP PREEMPT Tue Aug 25 10:01:34 UTC 2020

[ 0.000000] Machine model: Freescale S32G275

[ 0.000000] earlycon: linflex0 at MMIO 0x00000000401c8000 (options '115200n8')

[ 0.000000] bootconsole [linflex0] enabled

[ 0.000000] cma: Reserved 256 MiB at 0x00000000cfc00000

[ 0.000000] random: get_random_bytes called from start_kernel+0x94/0x3f0 with crng_init=0

[ 0.000000] percpu: Embedded 21 pages/cpu s48920 r8192 d28904 u86016

[ 0.000000] Detected VIPT I-cache on CPU0

[ 0.000000] CPU features: enabling workaround for ARM erratum 845719

[ 0.000000] CPU features: detected: Kernel page table isolation (KPTI)

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 900415

[ 0.000000] Kernel command line: console=ttyLF0,115200 root=/dev/mmcblk0p2 rootwait rw earlycon nohz=off coherent_pool=64M

[ 0.000000] Dentry cache hash table entries: 524288 (order: 10, 4194304 bytes)

[ 0.000000] Inode-cache hash table entries: 262144 (order: 9, 2097152 bytes)

[ 0.000000] software IO TLB: mapped [mem 0xcbc00000-0xcfc00000] (64MB)

[ 0.000000] Memory: 3151736K/3651584K available (6078K kernel code, 368K rwdata, 2024K rodata, 448K init, 215K bss, 237704K reserved, 262144K cma-reserved)

[ 0.000000] rcu: Preemptible hierarchical RCU implementation.

[ 0.000000] Tasks RCU enabled.

[ 0.000000] NR_IRQS: 64, nr_irqs: 64, preallocated irqs: 0

[ 0.000000] GICv3: Distributor has no Range Selector support

[ 0.000000] GICv3: no VLPI support, no direct LPI support

[ 0.000000] ITS: No ITS available, not enabling LPIs

[ 0.000000] GICv3: CPU0: found redistributor 0 region 0:0x0000000050880000

[ 0.000000] arch_timer: cp15 timer(s) running at 5.00MHz (virt).

[ 0.000000] clocksource: arch_sys_counter: mask: 0xffffffffffffff max_cycles: 0x127350b88, max_idle_ns: 440795202120 ns

[ 0.000005] sched_clock: 56 bits at 5MHz, resolution 200ns, wraps every 4398046511100ns

[ 0.008351] Console: colour dummy device 80x25

[ 0.012468] Calibrating delay loop (skipped), value calculated using timer frequency.. 10.00 BogoMIPS (lpj=20000)

[ 0.022689] pid_max: default: 32768 minimum: 301

[ 0.027433] Mount-cache hash table entries: 8192 (order: 4, 65536 bytes)

[ 0.033989] Mountpoint-cache hash table entries: 8192 (order: 4, 65536 bytes)

[ 0.065168] ASID allocator initialised with 32768 entries

[ 0.078243] rcu: Hierarchical SRCU implementation.

[ 0.106732] smp: Bringing up secondary CPUs ...

[ 0.151077] Detected VIPT I-cache on CPU1

[ 0.151111] GICv3: CPU1: found redistributor 1 region 0:0x00000000508a0000

[ 0.151147] CPU1: Booted secondary processor 0x0000000001 [0x410fd034]

[ 0.191123] Detected VIPT I-cache on CPU2

[ 0.191151] GICv3: CPU2: found redistributor 100 region 0:0x00000000508c0000

[ 0.191179] CPU2: Booted secondary processor 0x0000000100 [0x410fd034]

[ 0.231190] Detected VIPT I-cache on CPU3

[ 0.231209] GICv3: CPU3: found redistributor 101 region 0:0x00000000508e0000

[ 0.231225] CPU3: Booted secondary processor 0x0000000101 [0x410fd034]

[ 0.231310] smp: Brought up 1 node, 4 CPUs

[ 0.287500] SMP: Total of 4 processors activated.

[ 0.292184] CPU features: detected: GIC system register CPU interface

[ 0.298610] CPU features: detected: 32-bit EL0 Support

[ 0.306755] CPU: All CPU(s) started at EL1

[ 0.310521] alternatives: patching kernel code

[ 0.315555] devtmpfs: initialized

[ 0.322790] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 7645041785100000 ns

[ 0.332215] futex hash table entries: 1024 (order: 4, 65536 bytes)

[ 0.344747] pinctrl core: initialized pinctrl subsystem

[ 0.350441] NET: Registered protocol family 16

[ 0.355564] vdso: 2 pages (1 code @ (____ptrval____), 1 data @ (____ptrval____))

[ 0.392905] DMA: preallocated 65536 KiB pool for atomic allocations

[ 0.398961] Serial: AMBA PL011 UART driver

[ 0.418631] HugeTLB registered 2.00 MiB page size, pre-allocated 0 pages

[ 0.430451] vgaarb: loaded

[ 0.433060] SCSI subsystem initialized

[ 0.436769] usbcore: registered new interface driver usbfs

[ 0.442312] usbcore: registered new interface driver hub

[ 0.447384] usbcore: registered new device driver usb

[ 0.453176] pps_core: LinuxPPS API ver. 1 registered

[ 0.457793] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

[ 0.467201] PTP clock support registered

[ 0.471596] clocksource: Switched to clocksource arch_sys_counter

[ 0.484113] NET: Registered protocol family 2

[ 0.488818] tcp_listen_portaddr_hash hash table entries: 2048 (order: 3, 32768 bytes)

[ 0.496354] TCP established hash table entries: 32768 (order: 6, 262144 bytes)

[ 0.503842] TCP bind hash table entries: 32768 (order: 7, 524288 bytes)

[ 0.510687] TCP: Hash tables configured (established 32768 bind 32768)

[ 0.517015] UDP hash table entries: 2048 (order: 4, 65536 bytes)

[ 0.522981] UDP-Lite hash table entries: 2048 (order: 4, 65536 bytes)

[ 0.529527] NET: Registered protocol family 1

[ 0.533974] RPC: Registered named UNIX socket transport module.

[ 0.539558] RPC: Registered udp transport module.

[ 0.544245] RPC: Registered tcp transport module.

[ 0.548927] RPC: Registered tcp NFSv4.1 backchannel transport module.

[ 0.555533] Unpacking initramfs...

[ 0.558752] Initramfs unpacking failed: junk in compressed archive

[ 0.608954] Freeing initrd memory: 98304K

[ 0.614005] workingset: timestamp_bits=62 max_order=20 bucket_order=0

[ 0.620989] fuse init (API version 7.27)

[ 0.625222] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 250)

[ 0.632285] io scheduler noop registered

[ 0.636187] io scheduler deadline registered

[ 0.640470] io scheduler cfq registered (default)

[ 0.645129] io scheduler mq-deadline registered

[ 0.649637] io scheduler kyber registered

[ 0.654050] s32g275-siul2-pinctrl 4009c240.siul2-pinctrl0: initialized s32 pinctrl driver

[ 0.662296] s32g275-siul2-pinctrl 44010400.siul2-pinctrl1: initialized s32 pinctrl driver

[ 0.677252] s32gen1-pcie 40400000.pcie: Configuring as RootComplex

[ 0.683162] s32gen1-pcie 40400000.pcie: Allocated line 0 for interrupt 66 (msi)

[ 0.690394] s32gen1-pcie 40400000.pcie: host bridge /pcie@40400000 ranges:

[ 0.697258] s32gen1-pcie 40400000.pcie: IO 0x5800003000..0x5800012fff -> 0x00000000

[ 0.705159] s32gen1-pcie 40400000.pcie: MEM 0x5800013000..0x5840012fff -> 0x00013000

[ 1.711594] s32gen1-pcie 40400000.pcie: Phy link never came up

[ 2.715593] s32gen1-pcie 40400000.pcie: Phy link never came up

[ 2.721209] s32gen1-pcie 40400000.pcie: PCI host bridge to bus 0000:00

[ 2.727606] pci_bus 0000:00: root bus resource [bus 00-ff]

[ 2.733071] pci_bus 0000:00: root bus resource [io 0x0000-0xffff]

[ 2.739231] pci_bus 0000:00: root bus resource [mem 0x5800013000-0x5840012fff] (bus address [0x00013000-0x40012fff])

[ 2.753103] pci 0000:00:00.0: BAR 0: assigned [mem 0x5800100000-0x58001fffff 64bit pref]

[ 2.760871] pci 0000:00:00.0: BAR 6: assigned [mem 0x5800020000-0x580002ffff pref]

[ 2.768409] pci 0000:00:00.0: PCI bridge to [bus 01-ff]

[ 2.773976] pcieport 0000:00:00.0: Signaling PME with IRQ 92

[ 2.779439] pcieport 0000:00:00.0: AER enabled with IRQ 92

[ 2.785178] s32gen1-pcie 44100000.pcie: u-boot did not initialize PCIE PHY; is u-boot compiled with PCIE support?

[ 2.796282] 401c8000.serial: ttyLF0 at MMIO 0x401c8000 (irq = 30, base_baud = 7812500) is a FSL_LINFLEX

[ 2.807429] console [ttyLF0] enabled

[ 2.807429] console [ttyLF0] enabled

[ 2.814711] bootconsole [linflex0] disabled

[ 2.814711] bootconsole [linflex0] disabled

[ 2.823540] 401cc000.serial: ttyLF1 at MMIO 0x401cc000 (irq = 31, base_baud = 7812500) is a FSL_LINFLEX

[ 2.833381] 402bc000.serial: ttyLF2 at MMIO 0x402bc000 (irq = 57, base_baud = 7812500) is a FSL_LINFLEX

[ 2.847880] libphy: Fixed MDIO Bus: probed

[ 2.852463] vcan: Virtual CAN interface driver

[ 2.857005] slcan: serial line CAN interface driver

[ 2.861981] slcan: 10 dynamic interface channels.

[ 2.866780] CAN device driver interface

[ 2.871567] flexcan 401b4000.flexcan: device registered (reg_base=(____ptrval____), irq(s):

[ 2.880094] flexcan 401b4000.flexcan: 26

[ 2.884186] flexcan 401b4000.flexcan: 27

[ 2.888282] flexcan 401b4000.flexcan: 28

[ 2.892373] flexcan 401b4000.flexcan: 29

[ 2.896464] flexcan 401b4000.flexcan: )

[ 2.901043] flexcan 402a8000.flexcan: device registered (reg_base=(____ptrval____), irq(s):

[ 2.909570] flexcan 402a8000.flexcan: 49

[ 2.913662] flexcan 402a8000.flexcan: 50

[ 2.917758] flexcan 402a8000.flexcan: 51

[ 2.921849] flexcan 402a8000.flexcan: 52

[ 2.925943] flexcan 402a8000.flexcan: )

[ 2.930403] flexcan 402b2000.flexcan: device registered (reg_base=(____ptrval____), irq(s):

[ 2.938925] flexcan 402b2000.flexcan: 53

[ 2.943017] flexcan 402b2000.flexcan: 54

[ 2.947112] flexcan 402b2000.flexcan: 55

[ 2.951202] flexcan 402b2000.flexcan: 56

[ 2.955296] flexcan 402b2000.flexcan: )

[ 2.959458] e1000e: Intel(R) PRO/1000 Network Driver - 3.2.6-k

[ 2.965411] e1000e: Copyright(c) 1999 - 2015 Intel Corporation.

[ 2.972162] s32cc-dwmac 4033c000.ethernet: PTP uses main clock

[ 2.978119] s32cc-dwmac 4033c000.ethernet: no reset control found

[ 2.984348] s32cc-dwmac 4033c000.ethernet: phy mode set to RGMII

[ 2.990598] s32cc-dwmac 4033c000.ethernet: User ID: 0x10, Synopsys ID: 0x51

[ 2.997708] s32cc-dwmac 4033c000.ethernet: DWMAC4/5

[ 3.002776] s32cc-dwmac 4033c000.ethernet: DMA HW capability register supported

[ 3.010231] s32cc-dwmac 4033c000.ethernet: RX Checksum Offload Engine supported

[ 3.017681] s32cc-dwmac 4033c000.ethernet: TX Checksum insertion supported

[ 3.024693] s32cc-dwmac 4033c000.ethernet: Wake-Up On Lan supported

[ 3.031111] s32cc-dwmac 4033c000.ethernet: Enabled workarounds for s32g274a platform

[ 3.039012] s32cc-dwmac 4033c000.ethernet: Enable RX Mitigation via HW Watchdog Timer

[ 3.047005] s32cc-dwmac 4033c000.ethernet (unnamed net_device) (uninitialized): device MAC address b2:87:c5:05:03:51

[ 3.057732] s32cc-dwmac 4033c000.ethernet: Enabling HW TC (entries=256, max_off=256)

[ 3.065723] libphy: stmmac: probed

[ 3.069942] mdio_bus stmmac-0: MDIO device at address 4 is missing.

[ 3.076566] mdio_bus stmmac-0: MDIO device at address 5 is missing.

[ 3.083183] mdio_bus stmmac-0: MDIO device at address 6 is missing.

[ 3.089805] mdio_bus stmmac-0: MDIO device at address 7 is missing.

[ 3.096702] usbcore: registered new interface driver asix

[ 3.102259] usbcore: registered new interface driver ax88179_178a

[ 3.108505] usbcore: registered new interface driver cdc_ether

[ 3.114488] usbcore: registered new interface driver net1080

[ 3.120294] usbcore: registered new interface driver cdc_subset

[ 3.126368] usbcore: registered new interface driver zaurus

[ 3.132096] usbcore: registered new interface driver cdc_ncm

[ 3.137903] usbcore: registered new interface driver qmi_wwan

[ 3.143961] ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

[ 3.150624] ehci-pci: EHCI PCI platform driver

[ 3.155231] usbcore: registered new interface driver cdc_wdm

[ 3.161037] usbcore: registered new interface driver uas

[ 3.166502] usbcore: registered new interface driver usb-storage

[ 3.172716] usbcore: registered new interface driver option

[ 3.178429] usbserial: USB Serial support registered for GSM modem (1-port)

[ 3.199421] ci_hdrc ci_hdrc.0: EHCI Host Controller

[ 3.204545] ci_hdrc ci_hdrc.0: new USB bus registered, assigned bus number 1

[ 3.231610] ci_hdrc ci_hdrc.0: USB 2.0 started, EHCI 1.00

[ 3.237248] usb usb1: New USB device found, idVendor=1d6b, idProduct=0002, bcdDevice= 4.19

[ 3.245680] usb usb1: New USB device strings: Mfr=3, Product=2, SerialNumber=1

[ 3.253045] usb usb1: Product: EHCI Host Controller

[ 3.258024] usb usb1: Manufacturer: Linux 4.19.59-rt24+ged566620fe59 ehci_hcd

[ 3.265299] usb usb1: SerialNumber: ci_hdrc.0

[ 3.270158] hub 1-0:1.0: USB hub found

[ 3.274009] hub 1-0:1.0: 1 port detected

[ 3.279363] s32gen1-rtc 40060000.rtc: rtc core: registered s32gen1_rtc as rtc0

[ 3.287677] sdhci: Secure Digital Host Controller Interface driver

[ 3.293980] sdhci: Copyright(c) Pierre Ossman

[ 3.298424] sdhci-pltfm: SDHCI platform and OF driver helper

[ 3.335639] mmc0: SDHCI controller on 402f0000.usdhc [402f0000.usdhc] using ADMA

[ 3.343511] usbcore: registered new interface driver usbhid

[ 3.350217] usbhid: USB HID core driver

[ 3.354483] NET: Registered protocol family 10

[ 3.360292] Segment Routing with IPv6

[ 3.364089] sit: IPv6, IPv4 and MPLS over IPv4 tunneling driver

[ 3.370606] NET: Registered protocol family 17

[ 3.375154] can: controller area network core (rev 20170425 abi 9)

[ 3.381881] NET: Registered protocol family 29

[ 3.386451] can: raw protocol (rev 20170425)

[ 3.390809] can: broadcast manager protocol (rev 20170425 t)

[ 3.396588] can: netlink gateway (rev 20170425) max_hops=1

[ 3.396646] mmc0: new high speed SDHC card at address 5048

[ 3.408886] mmcblk0: mmc0:5048 SD16G 14.4 GiB

[ 3.413449] s32gen1-rtc 40060000.rtc: setting system clock to 2018-08-10 18:00:00 UTC (1533924000)

[ 3.424338] mmcblk0: p1 p2

[ 3.432587] EXT4-fs (mmcblk0p2): mounting ext3 file system using the ext4 subsystem

[ 3.564012] EXT4-fs (mmcblk0p2): recovery complete

[ 3.572759] EXT4-fs (mmcblk0p2): mounted filesystem with ordered data mode. Opts: (null)

[ 3.580548] VFS: Mounted root (ext3 filesystem) on device 179:2.

[ 3.586575] devtmpfs: mounted

[ 3.589629] Freeing unused kernel memory: 448K

[ 3.593954] Run /sbin/init as init process

INIT: version 2.88 booting

[ 3.712010] random: fast init done

Starting udev

[ 3.999267] udevd[797]: starting version 3.2.8

[ 4.008995] random: udevd: uninitialized urandom read (16 bytes read)

[ 4.016322] random: udevd: uninitialized urandom read (16 bytes read)

[ 4.022469] random: udevd: uninitialized urandom read (16 bytes read)

[ 4.057252] udevd[798]: starting eudev-3.2.8

[ 4.608718] pfeng: loading out-of-tree module taints kernel.

[ 4.639285] pfeng 46000000.pfe: pfeng, ethernet driver loading ...

[ 4.645189] pfeng 46000000.pfe: Found reserved memory at p0x83400000 size 0xc00000

[ 4.652905] pfeng 46000000.pfe: Cbus addr 0x46000000 size 0x1000000

[ 4.658939] pfeng 46000000.pfe: firmware-name: s32g_pfe_class.fw

[ 4.665015] pfeng 46000000.pfe: HIF channel 0 in SC mode

[ 4.670227] pfeng 46000000.pfe: pfe0 linked to EMAC 0

[ 4.675259] pfeng 46000000.pfe: HIF channel 2 in SC mode

[ 4.680547] pfeng 46000000.pfe: pfe2 linked to EMAC 2

[ 4.685586] pfeng 46000000.pfe: TX clocks for interface pfe2 installed

[ 4.692086] pfeng 46000000.pfe: HIF channels mask: 0x0005

[ 4.697477] pfeng 46000000.pfe: Interface selected: EMAC0: 0x4 EMAC1: 0xffffffed EMAC2: 0x8

[ 4.718907] pfeng 46000000.pfe: Firmware: s32g_pfe_class.fw [size: 166088 bytes]

[ 4.725991] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:2718] INF: PFE CBUS p0x(____ptrval____) mapped @ v0x(____ptrval____)

[ 4.744578] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:2769] INF: Detected per block IRQ mode (S32G)

[ 4.756488] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:1381] INF: BMU1 buffer base: p0x(____ptrval____)

[ 4.770845] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:1428] INF: BMU2 buffer base: p0x(____ptrval____) (2097152 bytes)

[ 4.786777] [/usr/src/debug/pfe/0.8.0-r0/git/sw/oal/.//src/oal_irq_linux.c:156] INF: register IRQ 85 by name 'PFE BMU IRQ'

[ 4.797626] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_bmu_csr.c:117] INF: BMU_EMPTY_INT (BMU @ p0x(____ptrval____)). Pool ready.

[ 4.810671] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_bmu_csr.c:117] INF: BMU_EMPTY_INT (BMU @ p0x(____ptrval____)). Pool ready.

[ 4.894305] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:1779] INF: Firmware .elf detected

[ 4.905177] [/usr/src/debug/pfe/0.8.0-r0/git/sw/elf/src/elf.c:1379] INF: ELF_Open: File format: Elf32

[ 4.914375] [/usr/src/debug/pfe/0.8.0-r0/git/sw/elf/src/elf.c:1380] INF: ELF_Open: File endian: Alien (Big)

[ 4.924123] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:1788] INF: Uploading CLASS firmware

[ 4.935472] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 4.950316] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 4.964705] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 4.979092] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 4.993477] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 5.007866] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 5.022273] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 5.036663] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 5.051046] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1738] INF: [FW VERSION] 0.8.0, Build: Mar 31 2020, 11:41:35 (c768f3e), ID: 0x31454650

[ 5.064955] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1747] INF: [PE 0 MMAP]

[ 5.064955] DMEM Heap Base: 0x20001150 (11952 bytes)

[ 5.064955] PHY IF Base : 0x20000aac (288 bytes)

[ 5.084143] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_emac_csr.c:308] INF: The PHY mode selection is done using a HW interface. See the 'phy_intf_sel' signal.

[ 5.100102] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_emac_csr.c:308] INF: The PHY mode selection is done using a HW interface. See the 'phy_intf_sel' signal.

[ 5.115924] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_emac_csr.c:308] INF: The PHY mode selection is done using a HW interface. See the 'phy_intf_sel' signal.

[ 5.131597] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:2149] INF: SAFETY instance created

[ 5.142830] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:2163] INF: Watchdog instance created

[ 5.155192] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:1913] INF: Routing table created, Hash Table @ p(____ptrval____), Pool @ p(____ptrva(65536 bytes)

[ 5.280190] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_l2br.c:643] INF: Fall-back bridge domain @ 0x20000a98 (class)

[ 5.293618] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:2913] INF: Enabling the CLASS block

[ 5.364627] pfeng 46000000.pfe pfe0 (uninitialized): setting MAC addr: 00:01:be:be:ef:11

[ 5.372937] pfeng 46000000.pfe pfe0: registered

[ 5.400167] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_hif_drv/src/pfe_hif_drv_sc.c:320] INF: Attempt to register HIF client: pfe0

[ 5.411299] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_hif_drv/src/pfe_hif_drv_sc.c:385] INF: HIF client pfe0 id 0 registered

[ 5.422440] pfeng 46000000.pfe pfe0: Register HIF client pfe0 for logif (____ptrval____)

[ 5.430444] pfeng 46000000.pfe pfe2 (uninitialized): setting MAC addr: 00:01:be:be:ef:33

[ 5.438896] pfeng 46000000.pfe pfe2: registered

[ 5.468519] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_hif_drv/src/pfe_hif_drv_sc.c:320] INF: Attempt to register HIF client: pfe2

[ 5.479651] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_hif_drv/src/pfe_hif_drv_sc.c:385] INF: HIF client pfe2 id 1 registered

[ 5.490788] pfeng 46000000.pfe pfe2: Register HIF client pfe2 for logif (____ptrval____)

[ 5.498865] libphy: PFEng Ethernet MDIO: probed

[ 5.503428] mdio_bus PFEng Ethernet MDIO.pfe2: MDIO device at address 1 is missing.

[ 5.511055] mdio_bus PFEng Ethernet MDIO.pfe2: MDIO device at address 2 is missing.

[ 5.579136] loading NXP PHY driver: [autonomous mode]

[ 5.677591] sja1105pqrs spi1.0: Loading SJA1105P SPI driver

[ 5.682940] sja1105pqrs spi1.0: Detected device id is invalid: ffffffff

[ 5.689435] sja1105pqrs spi1.0: SJA1105P SPI Failed to read Device Id

[ 5.712578] EXT4-fs (mmcblk0p2): re-mounted. Opts: (null)

Fri Aug 28 01:21:01 UTC 2020

[ 5.995835] urandom_read: 3 callbacks suppressed

[ 5.995844] random: dd: uninitialized urandom read (512 bytes read)

INIT: Entering runlevel: 5

Configuring network interfaces... ifup: don't have all variables for eth0/inet

Starting syslogd/klogd: done

Starting random number generator daemon[ 6.197407] random: rngd: uninitialized urandom read (4 bytes read)

[ 6.203438] random: rngd: uninitialized urandom read (4 bytes read)

.

[ 6.211508] random: crng init done

[ 6.214604] random: 1 urandom warning(s) missed due to ratelimiting

Starting OpenBSD Secure Shell server: sshd

done.

Auto Linux BSP 1.0 s32g274ardb /dev/ttyLF0

s32g274ardb login:

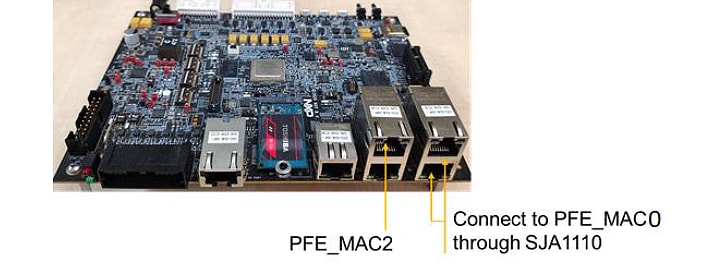

S32G-VNP-RDB3 Setup for Testing

S32G-VNP-RDB3 Setup for Testing

Connect corresponding ports according to which PFE interface is used, then power up the board for test.

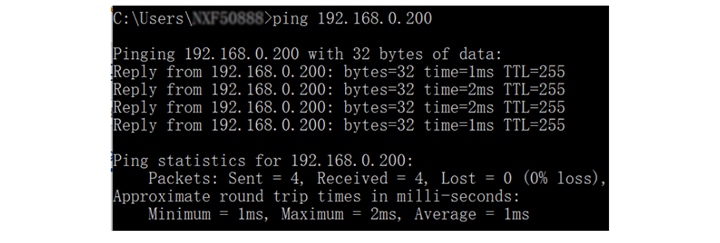

Do a ping test to confirm conection:

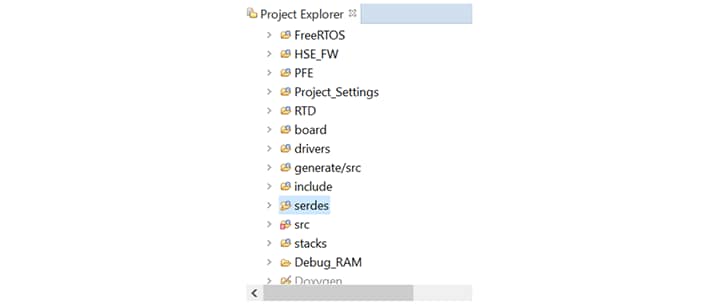

Extract the serdes folder and add to project directory. Right click folder in Project Explorer and select Build path → Add to → Debug_RAM to include serdes source code to project:

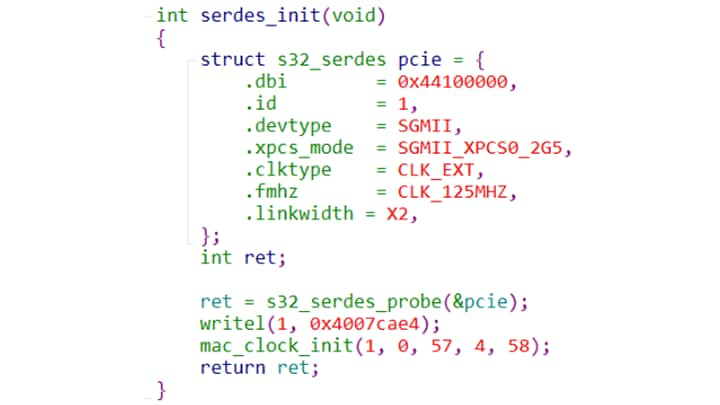

Change the initialization parameters of serdes according to board setup:

Call serdes_init() before Eth_43_PFE_init()

serdes_init();

oal_mm_init(NULL);

Eth_43_PFE_Init(NULL_PTR);Design Resources

Support

Training

- Automating the Development of AI-based DL Vehicle Health Management (VHM) Solutions on the S32G

- Transitioning to Safe and Secure Zonal Architectures with the S32G

- Designing Secure Automotive Gateway Solutions Using Time-Sensitive Network (TSN) Protocol on the S32G

- Developing In-Vehicle Cloud Service Applications Using the AWS Connected Mobility Solution and the S32G

- Advanced In-Vehicle Cloud Service Applications Using the AWS Connected Mobility Solution

- Orchestrating Automotive OTA Software Updates and Data Management Using Airbiquity OTAmatic® on the S32G

- Enabling Connected Intelligent Vehicles with The Fusion Project Machine Learning-Based Data Lifecycle

Forums

Connect with other engineers and get expert advice on designing with the NXP S32G VNP RDB3 in its dedicated community.