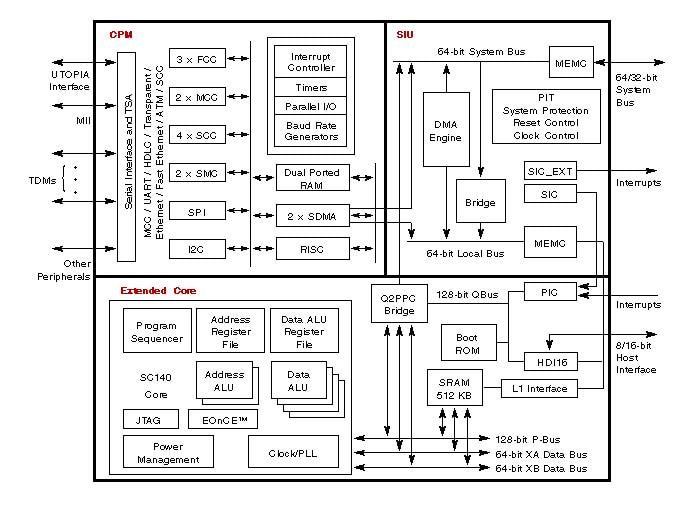

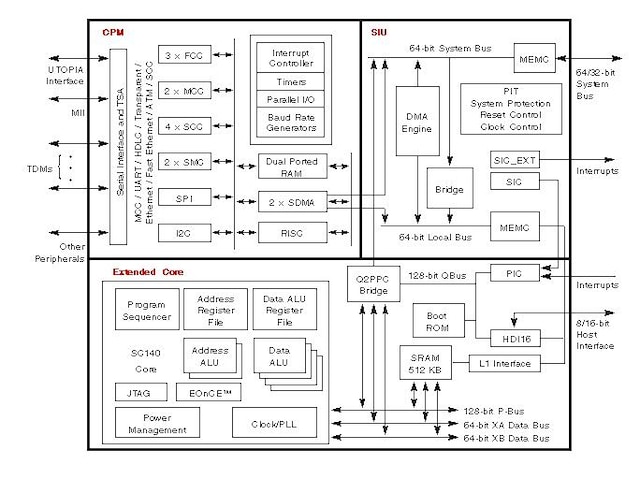

The NXP® MSC8103 Integrated Digital Signal Processor (DSP) is

based on the SC140 DSP core. This versatile chip integrates on a single device

the high-performance StarCore® 140 (SC140) four-ALU

(Arithmetic Logic Unit) DSP core along with 512 KB of on-chip memory, a

Communications Processor Module (CPM), a 64-bit 60x-compatible system bus, a

flexible System Integration Unit (SIU), and a 16-channel DMA engine. With its

four ALU core, the MSC8103 can execute up to four multiply-accumulate (MAC)

operations in a single clock cycle. The MSC8103 CPM is a 32-bit RISC-based

communications protocol engine that can network to Time-Division Multiplexed

(TDM) highways, Ethernet, and Asynchronous Transfer mode (ATM) backbones. The

MSC8103 60x-compatible bus interface facilitates its connection to

system architectures. The large on-chip memory, 512 KB, reduces

the need for off-chip program and data memories. The MSC8103 device offers

1200 MMACS performance using an internal 300 MHz clock with a 1.6 V core and

independent 3.3 V input/output (I/O).

The MSC8103 device is very similar to the MSC8101; the MSC8101

documentation listed on this page will be helpful to MSC8103 developers. The

MSC8103 device uses the MSC8101 tools listed on this page.

Target Applications

The MSC8103 device targets applications requiring very high performance, very

large amounts of on-chip memory, and such networking capabilities as:

- Third-generation wideband wireless infrastructure systems

- IP Telephony systems

- Multi-channel modem banks

- Multi-channel xDSL

Development Tools NOTE:

For information on the compiler, linker, assembler tools that have been

developed for StarCore products, click on "Related Links" and visit

the vendor site.

Design Tools NOTE:

A library of software modules and MSC8101 device driver examples is available

to accelerate bringing MSC8103 products to market.