Design Files

1 design file

Receive the full breakdown. See the product footprint and more in the eCad file.

-

Printed Circuit Boards and Schematics

OrCAD Design Files for the MPC8544 and MPC8533

The MPC8533E PowerQUICC® III communications processor offers high level of integration and performance for Ethernet-only or PCIe interworking applications, such as enterprise networking and advanced multi-function printer (MFP) and imaging applications.

Access to the errata document for this device requires an NDA. Contact your local NXP® Sales Office or NXP Authorized Distributor.

Part numbers include: MPC8533EVJALFA, MPC8533EVJANGA, MPC8533EVJAQGA, MPC8533EVTALFA, MPC8533EVTANGA, MPC8533EVTARJA, MPC8533VJALFA, MPC8533VJAQGA, MPC8533VTALFA.

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Quick reference to our documentation types.

1-5 of 49 documents

Please wait while your secure files are loading.

1 design file

Receive the full breakdown. See the product footprint and more in the eCad file.

Please wait while your secure files are loading.

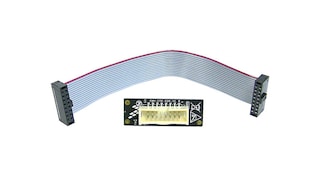

2 hardware offerings

Quick reference to our software types.

3 software files

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

5 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 11 engineering services

.png)

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

7 trainings

7 trainings

To find additional partner offerings that support this product, visit our Partner Marketplace.