The MSC8156E is based on the industry's highest-performance DSP core built on StarCore® technology and designed for the advanced processing requirements and capabilities of today's high-performance applications for the wireless broadband, medical imaging, aerospace, defense and advanced test and measurement markets. It delivers higher performance and power savings, leveraging 45 nm process technology in a highly integrated system-on-chip (SoC) to provide performance equivalent to a 6 GHz, single-core device. The MSC8156E helps equipment manufacturers create end products and services that integrate more functionality in a smaller hardware footprint.

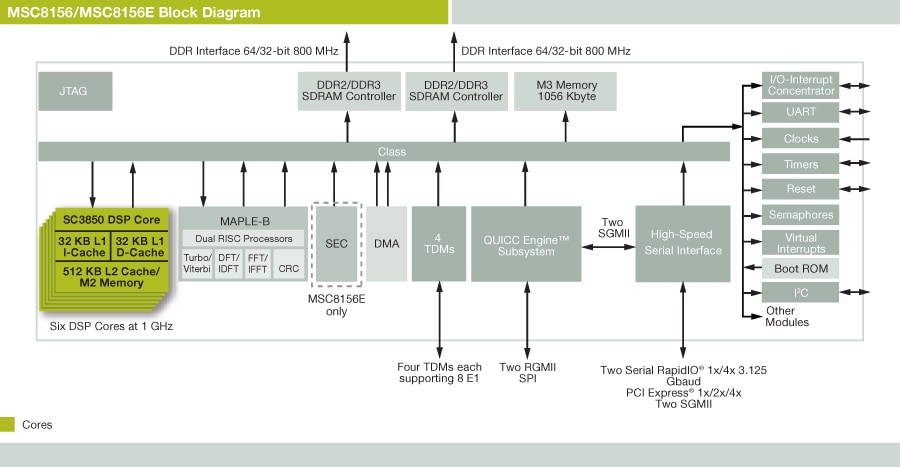

The MSC8156E DSP delivers a high level of performance and integration, combining six fully programmable enhanced SC3850 DSP cores, each running at up to 1 GHz. Developed by NXP® and integrated on-chip, the MAPLE-B accelerator supports hardware acceleration for Turbo and Viterbi channel decoding and for DFT/iDFT and FFT/iFFT algorithms. A high-performance internal RISC-based QUICC Engine® subsystem supports multiple networking protocols to guarantee reliable data transport over packet networks while significantly offloading processing from the DSP cores.

The MSC8156E embeds large internal memory and supports a variety of advanced high-speed interface types, including two RapidIO® interfaces, two gigabit Ethernet interfaces for network communications, a PCI Express® controller, two DDR controllers for high-speed, industry standard memory interface and four multi-channel TDM interfaces. The MSC8156E allows a high degree of scalability through pin compatibility with all MSC825x and MSC815x DSP devices.