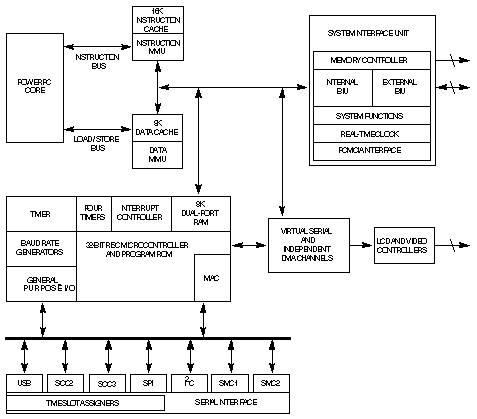

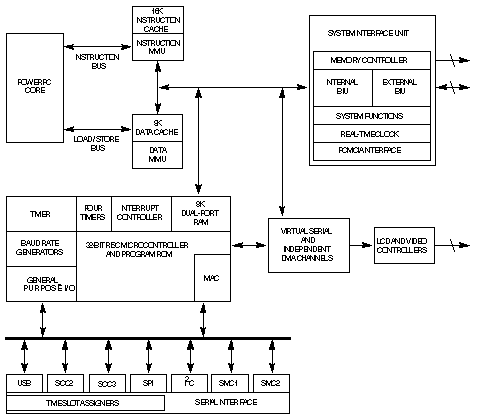

The MPC823e microprocessor is a versatile, one-chip integrated microprocessor and peripheral combination that can be used in a variety of electronic products. It particularly excels in low-power, portable, image capture and personal communication products. It is a version of the MPC823 microprocessor that provides enhanced performance with larger data and instruction caches. Like the MPC823, it has a universal serial bus (USB) interface and video display controller, as well as the existing LCD controller of the MPC823 (Rev A) device.

The MPC823e microprocessor integrates a high-performance embedded MPC8xx core with a communication processor module that uses a specialized RISC processor for imaging and communication. The communication processor module can perform embedded signal processing functions for image compression and decompression. It also supports seven serial channels--two serial communication controllers, two serial management controllers, one I²C port, one USB channel, and one serial peripheral interface.

This two-processor architecture consumes power more efficiently than traditional architectures because the communication processor module frees the core from peripheral tasks like imaging and communication.