Start Using KITFS86SKTFRDMEM Boards

Contents of this document

-

Out of the Box

-

Get Hardware

-

Configure Hardware

Sign in to save your progress. Don't have an account? Create one.

Purchase your KITFS86SKTFRDMEM: FS86 Safety SBC Programming Socket Board

1. Out of the Box

The NXP analog product development boards provide an easy-to-use platform for evaluating NXP products. The boards support a range of analog, mixed-signal and power solutions. They incorporate monolithic integrated circuits and system-in-package devices that use proven high-volume technology. NXP products offer longer battery life, a smaller form factor, reduced component counts, lower cost and improved performance in powering state-of-the-art systems.

This page will guide you through the process of setting up and using the KITFS86SKTFRDMEM board.

1.1 Kit Contents and Packing List

The contents include:

- Quick start guide

- Assembled and tested KITFS86SKTFRDMEM connected to a FRDM-KL25Z in an antistatic bag

- 3.0 ft USB-STD A to USB-B-mini cable

- Two connectors, terminal block plug, 2 pos., str. 3.81 mm

- Two connectors, terminal block plug, 3 pos., str. 3.81 mm

- Jumpers mounted on board

1.2 Additional Hardware

In addition to the kit contents, the following hardware is necessary or beneficial when working with this board:

- Power supply with a range of 8.0 V to 60 V and a current limit set initially to 1.0 A

1.3 Minimum System Requirements

This evaluation board requires a Windows PC workstation. Meeting these minimum specifications should produce positive results when working with this evaluation board:

- USB-enabled computer with Windows 7 or Windows 10

1.4 Software

Installing software is necessary to work with this evaluation board. All listed software is available on the evaluation board's information page at KITFS86SKTFRDMEM or from the provided link.

- NXP GUI for automotive PMIC families - latest version

2. Get Hardware

2.1 Board Features

- VBAT power supply connectors (Jack and Phoenix)

- VPRE output capability up to 1.0 A (socket limit)

- VBUCK 1.0 V to 3.3 V

- VBOOST 5.0 V to 6.0 V

- LDO1 1.5 V to 5.0 V

- LDO2 1.1 V to 5.0 V

- Ignition key switch

- FS0B external safety pin

- Embedded USB connection for easy connection to software NXP GUI (access to I²C-bus, IOs, RSTB, FS0B,

- INTB, Debug, MUX_OUT, regulators, register access, OTP emulation and programming)

- LEDs that indicate signals and regulator status

- Support OTP fuse capabilities

- Voltage monitoring jumper setting

2.2 Board Description

The KITFS86SKTFRDMEM provides flexibility to play with all the features of the device and make measurements on the main part of the application. The KL25Z MCU freedom board plugged on the board, combined with the NXP GUI software allows access to the registers in read and write mode. All regulators are accessible through connectors. Nonuser signal, like DC-DC switcher node is mapped on test points. Digital signals (I²C, RSTB, and so on) are accessible through connectors. Pin WAKE1 has a switch to control (ignition) them. A VBAT switch is available to power on or off the device. The main purpose of this kit is to burn the OTP configuration. This kit can be operated in emulation mode or in OTP mode. In emulation mode, as long as the power is supplied, the board configuration stays valid, however the fail-safe configuration is lost if the device goes into deep fail-safe. The OTP mode uses the fused configuration. The device can be fused two times. In OTP mode, the device always starts with the fused configuration, except if the user wants to overwrite the OTP configuration using emulation mode. This board is able to fuse the OTP without any extra tools or board.

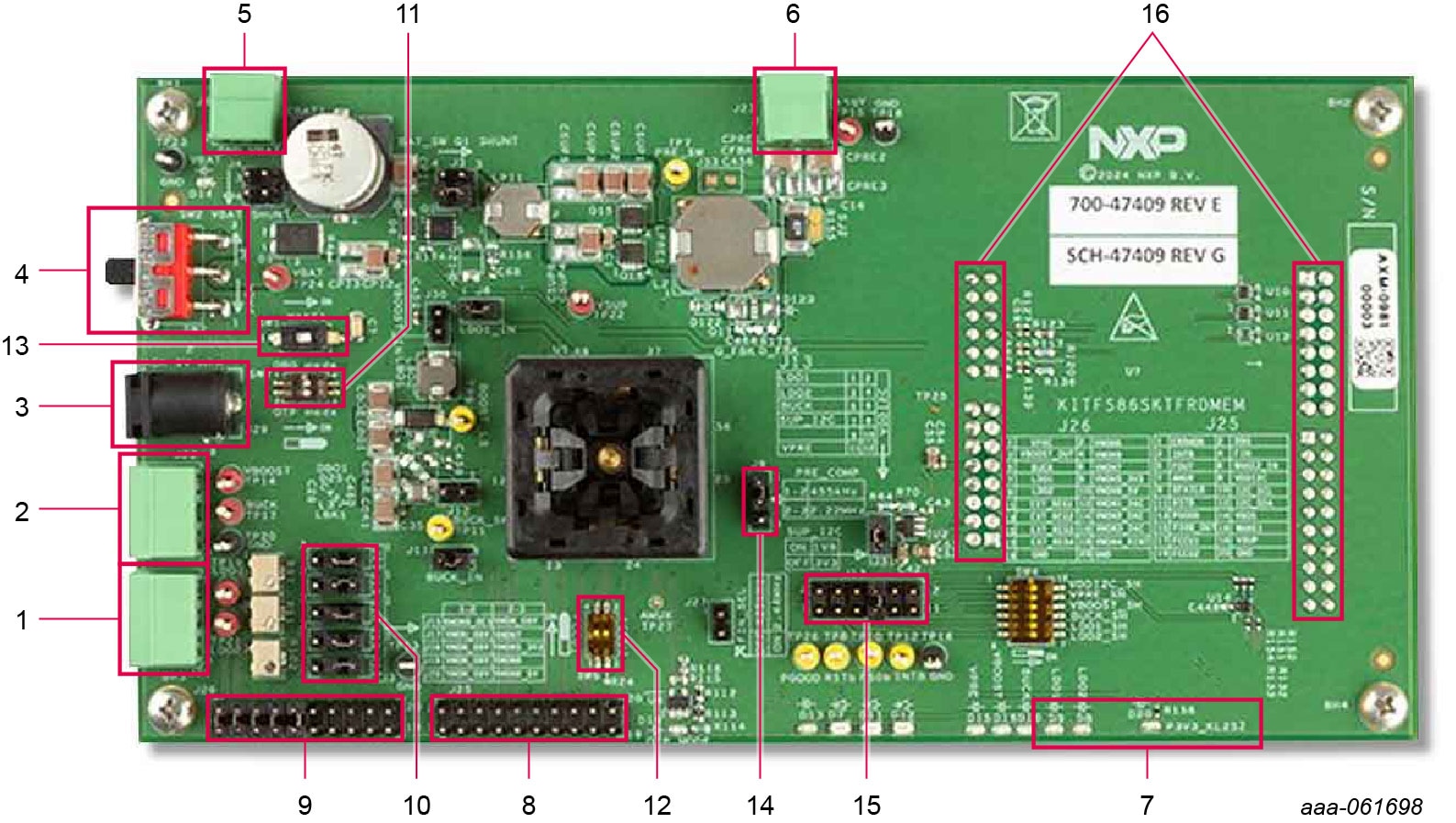

2.3 Board Components

| Number | Description |

|---|---|

| 1 | LDO1 / LDO2 power supply |

| 2 | BUCK / BOOST power supply |

| 3 | VBAT Jack connector |

| 4 |

VBAT three position switch

|

| 5 | VBAT Phoenix connector |

| 6 | VPRE power supply |

| 7 | USB connectors (Open SDA for MCU flash; KL25Z for NXP GUI control) |

| 8 | Debug connectivity. Access to FS8600 signals |

| 9 | External regulator connectors (to VMONx) |

| 10 | VMONx configuration (Choice between monitoring a regulator or a fixed 0.8 V) |

| 11 | OTP and DBG switch |

| 12 | FCCU switch |

| 13 | VPRE compensation network settings (455 kHz or 2.22 MHz) |

| 14 | VDDI2C selection |

| 17 | KL25Z freedom board connectors |

3. Configure Hardware

3.1 Configure Hardware

The device configuration can be changed twice. The programming steps are described in the NXP GUI for FS86 automotive family user manual available at NXP GUI for Automotive PMIC FamiliesNXP GUI for Automotive PMIC Families.

Figure 2 presents a typical hardware configuration incorporating the development board, power supply and Windows PC workstation.

To configure the hardware and workstation as illustrated in Figure 2, complete the following procedure:

- Install jumpers and switches for the configuration shown in Table 2

- Connect the Windows PC USB port to the KITFS86SKTFRDMEM development board using the provided USB 2.0 cable

- Set the DC power supply to 12 V and current limit to 1.0 A. With power turned Off, attach the DC power supply positive and negative output to VBAT Phoenix connector (

J6) - Turn On the power supply

- Put

SW2in TOP position

| Switch | Configuration | |||

|---|---|---|---|---|

| Normal mode | Debug mode entry | OTP mode entry | ||

| Operation | watchdog 2s window | watchdog window fully open | OTP emulation / programming and Debug mode entry | |

SW1 (WAKE1) |

close (WAKE1 high) | |||

SW2 (VBAT) |

middle position (VBAT OFF) | |||

SW7 (DBG_OTP) |

1-4 open (DBG mode OFF) 2-3 open (OTP mode OFF) |

2-3 close (OTP mode ON) | ||

|

2-3 open (OTP mode OFF) 1-4 close (DBG = 4.5 V) |

||||

To configure the hardware and workstation as illustrated in Figure 3, complete the following procedure:

- Install jumpers and switches for the configuration shown in Table 2

- Connect the Windows PC USB port to the KITFS86SKTFRDMEM development board using the provided USB 2.0 cable

- Set the DC power supply to 12 V and current limit to 1.0 A. With power turned off, attach the DC power supply positive and negative output to VBAT Phoenix connector (

J6) - Turn on the power supply

- Put SW2 in TOP position

At this step, if the product is in OTP mode entry configuration, all regulators are Off. The user can power up with an OTP configuration or configure the mirror registers before powering up. Power-up starts as soon as one of these three functions occurs:

SW7(2-3) is switched Off- OTP mode exit command is sent by I²C

- NXP GUI button "Exit OTP Mode" is clicked

Design Resources

Board Documents

Additional References

In addition to our FS86: Safety System Basis Chip For Domain Controller, Fit For ASIL B and D page, you may also want to visit:

- FS8500: Safety System Basis Chip for S32 Microcontrollers, Fit for ASIL D

- FS8400: Safety System Basis Chip for S32 Microcontrollers, Fit for ASIL B

- NXP GUI for Automotive PMIC Families

Application pages: