Getting Started with the TJA1103EVB Evaluation Board

Contents of this document

-

Out of the Box

-

Get Hardware

-

Configure Hardware

Sign in to save your progress. Don't have an account? Create one.

Purchase your TJA1103EVB

1. Out of the Box

The NXP analog product development boards provide an easy-to-use platform for evaluating NXP products. The boards support a range of analog, mixed-signal and power solutions. They incorporate monolithic integrated circuits and system-in-package devices that use proven high-volume technology. NXP products offer longer battery life, a smaller form factor, reduced component counts, lower cost and improved performance in powering state-of-the-art systems.

This page will guide you through the process of setting up and using the TJA1103EVB board.

1.1 Kit Content and Packing List

The TJA1103EVB contents include:

- Board: TJA1103EVB rev B

- Cable: UTP with 2x MATEnet connectors

1.2 Additional Hardware

In addition to the kit contents, the following hardware is necessary or beneficial when working with this board.

- Cable: USB-A to Micro-USB for power supply option A and USB communication to PHY

- Power adapter: 5.0 V to 15 V DC, min. 250 mA, 2.1 mm coaxial power connector for power supply option B

1.3 Software

The software used to communicate to the board via USB can be downloaded from NXP's website.

The software provides easy access to all settings within the PHY allowing interaction with all function modules. It is designed in such a way that basic functionality can be used via simple self explanatory dialogs and controls while at the same time giving access to all available registers, therefore not restricting the user to some predefined examples.

The following functions are supported by specifically guided dialogs:

- xMII / MDI configuration

- PHY status

- Loopback / test mode configuration

- TC10 wake/sleep

- BIST (internal frame generator/checker)

- FUSA (functional safety)

In addition, the following dialogs allow generic access:

- Global SMI access (PHY-address, register address and optional MMD (clause 45) configurable)

- Per-PHY SMI access (PHY-address predefined, register names automatically resolved)

- Per-PHY register table (interactive register description similar to data sheet with additional live view option)

2. Get Hardware

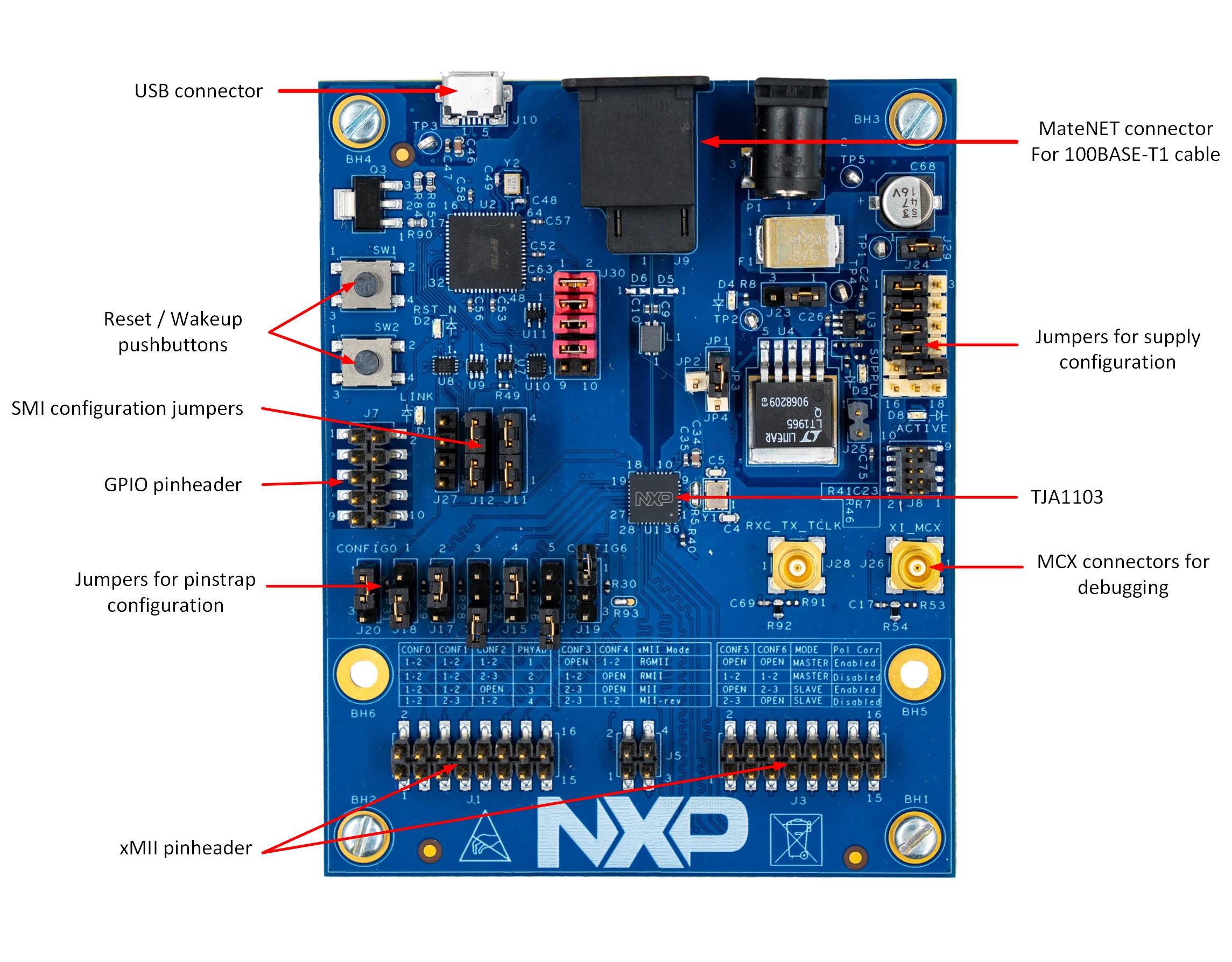

2.1 Board Features

- Multiple supply options

- Three operation modes: standalone, software controlled, external control/application integrated

- OA compliant MDI interface via Matenet connector

- xMII via pin header

- SMI via USB and pin header

- All host interface signals accessible via USB and pin header

- Clock in / TCLK out via MCX connectors

- Stackable for PHY-to-PHY operation

2.2 Board Description

The TJA1103EVB is intended to provide an easy way to get to know and start working with the TJA1103A PHY. The EVB is designed in such a way that all configuration options can be selected via jumpers and all logic pins can be accessed via pin headers. The onboard FTDI USB to SMI/JTAG/GPIO chip and the supply-via-USB option allows operation without any external components.

3. Configure Hardware

3.1 Configure Hardware

- Unpack the board

- Set jumper defaults

-

Choose supply variant

- 1-2: Supply via coaxial (barrel) connector

- 2-3: Supply via USB cable

-

Choose SMI connection variant

SetJ11andJ12to either of the following settings:- 1-2: Control PHY via software

-

3-4: Control PHY via external SMI connected either to

J11/J12orJ5

- Connect board via USB and/or coaxial connector

- Download the TJA1103EVB software, additional steps are explained in the README provided with the software

| Jumper number | Default configuration | Function |

|---|---|---|

J11 |

1-2, 3-4 | SMI routing |

J12 |

1-2, 3-4 | |

J20 |

1-2 | Pinstrap configuration |

J18 |

2-3 | |

J17 |

- | |

J16 |

- | |

J15 |

1-2 | |

J14 |

- | |

J19 |

- | |

JP1-4 |

1-3 | Adjustable supply voltage selector |

J23 |

2-3 | Input supply selector |

J25 |

- | LDO shutdown override |

Design Resources

Board Information

- Available to selected customers only (non-disclosure agreement (NDA) required), please contact your local NXP sales representative for more information.

References

In addition to our TJA1103: ASIL B Compliant 100BASE-T1 Ethernet PHY page.

Application Pages: