RoadLINK® SAF5400 Single Chip Modem for V2X

The SAF5100 is available in a Ball Grid Array (BGA) package occupying small Printed-Circuit Board (PCB) real estate and is suitable for multi-layer PCBs.

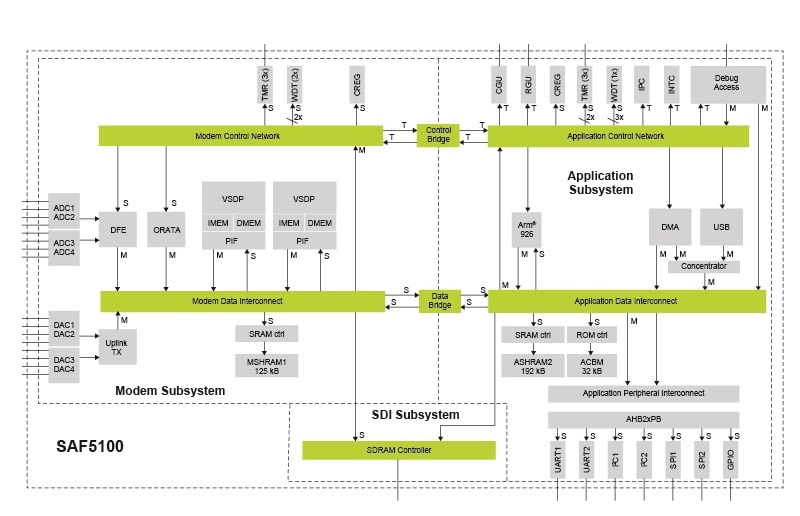

The SAF5100 this baseband processor includes Analog-to-Digital Converters (ADC) and Digital-to-Analog Converters (DAC) for interfacing with an external transceiver. Digital components included are:

The SAF5100 is available with an executable of a firmware comprising PHY/MAC (IEEE 802.11p and ETSI EN 302 663) and LLC (IEEE 1609.4 and ETSI EN 302 663) to be loaded into the RAM of the SAF5100.

Note: To see the product features close this window.

Quick reference to our documentation types

1 documents

Compact List

Please wait while your secure files are loading.

Please wait while your secure files are loading.

3 hardware offerings

3 hardware offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

1 engineering service

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

2 trainings