Hardware

4 hardware offerings

-

Evaluation and Development Boards

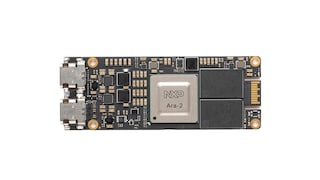

Evaluation and Development BoardsAra240 16GB M.2 Module

Active -

Evaluation and Development Boards

Evaluation and Development BoardsFRDM i.MX 8M Plus Development Board

Active -

Evaluation and Development Boards

Evaluation and Development BoardsAra240 USB Module: eTOPS for Gen AI Workloads

Preproduction -

Evaluation and Development Boards

Evaluation and Development BoardsFRDM i.MX 95 Development Board

Active