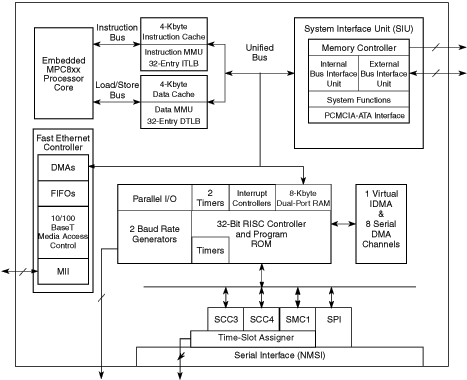

The MPC853T is an "ethernet-only" member of the MPC866 Family. Like the MPC866, the MPC853T is a 0.18 micron version of the PowerQUICC® Family and can operate up to a maximum of 100 MHz on the MPC8xx Core with a maximum of 66 MHz external bus. The MPC853T has a 1.8 V core and has a 3.3 V I/O operation with 5 V TTL compatibilty. The MPC853T Integrated Communications Controller is a versatile one-chip integrated microprocessor and peripheral combination that can be used in a variety of controller applications. The MPC853T is ideal for voice-enabled systems (TDM-based) and ethernet to ethernet applications such as line cards.

The MPC853T is a Power Architecture-based derivative of NXP® Semiconductors's Quad Integrated Communications Controller (PowerQUICC).. The CPU on the MPC853T is the MPC8xx core, a 32-bit microprocessor built on Power Architecture technology, incorporating memory management units (MMUs) and instruction and data caches.