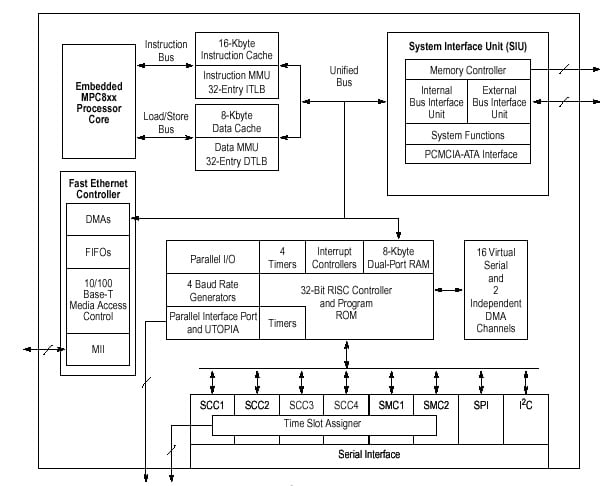

MPC866 PowerQUICC™ Family is a 0.18 micron version of the MPC862 PowerQUICC® Family and can operate up to 133 MHz on the MPC8xx core with a 66 MHz external bus. The MPC866 Family has a 1.8 V core and has a 3.3 V I/O operation with 5 V TTL compatibilty. The MPC866 Integrated Communications Controller Family is a versatile one-chip integrated microprocessor and peripheral combination that can be used in a variety of controller applications. It particularly excels in both communications and networking systems.

The MPC866 Family is a a Power Architecture-based derivative of Our Quad Integrated Communications Controller (PowerQUICC). The CPU on the MPC866 is the MPC8xx core, a 32-bit microprocessor built on Power Architecture technology, incorporating memory management units (MMUs) and instruction and data caches. The MPC866P is the superset of this family of devices.