Programmable Logic

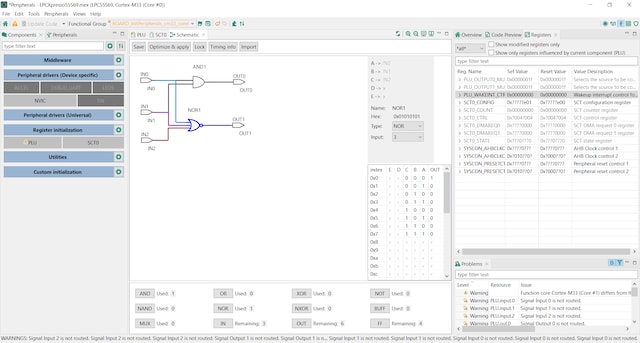

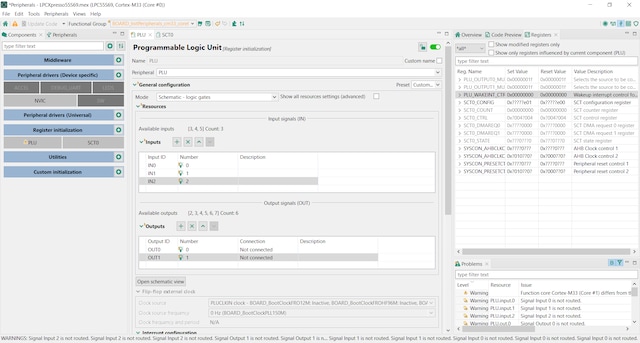

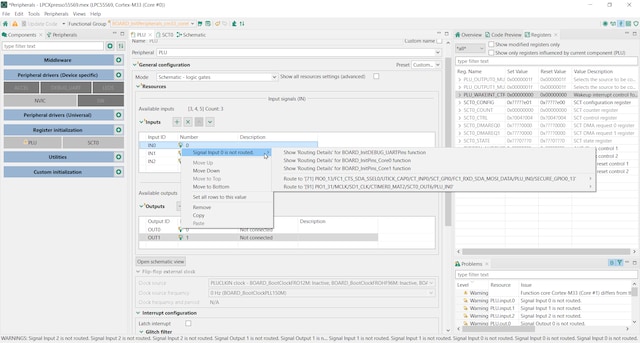

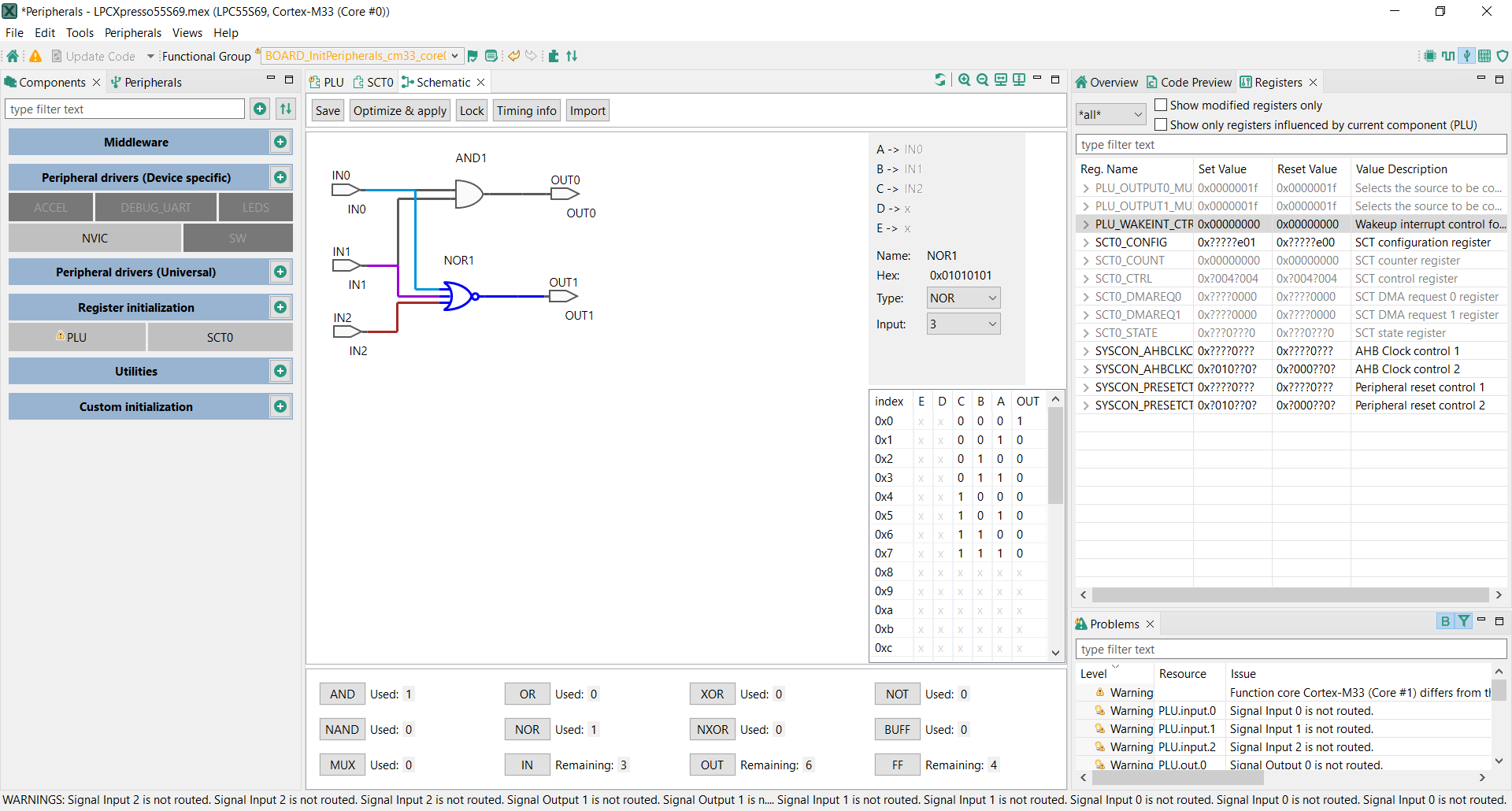

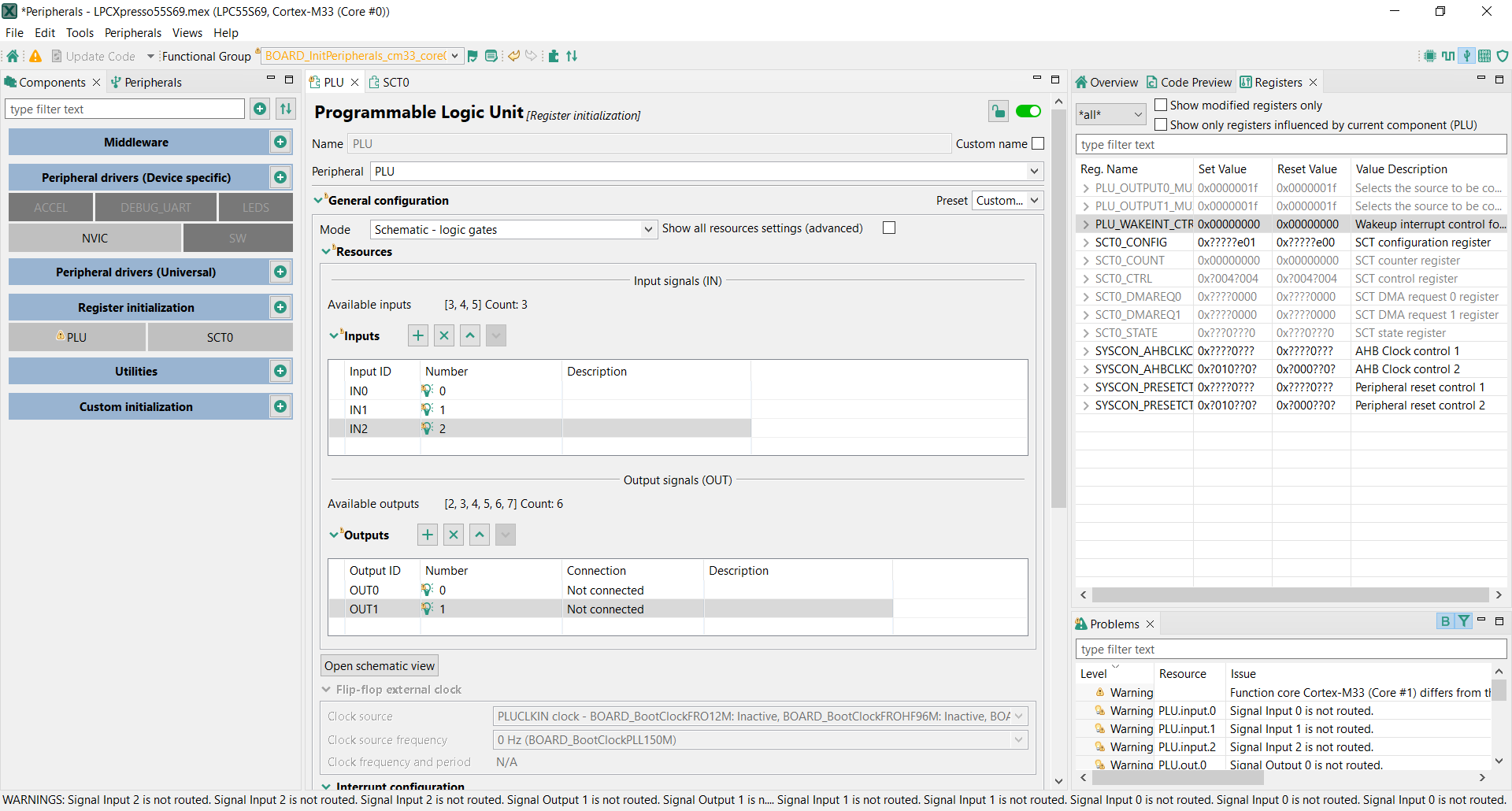

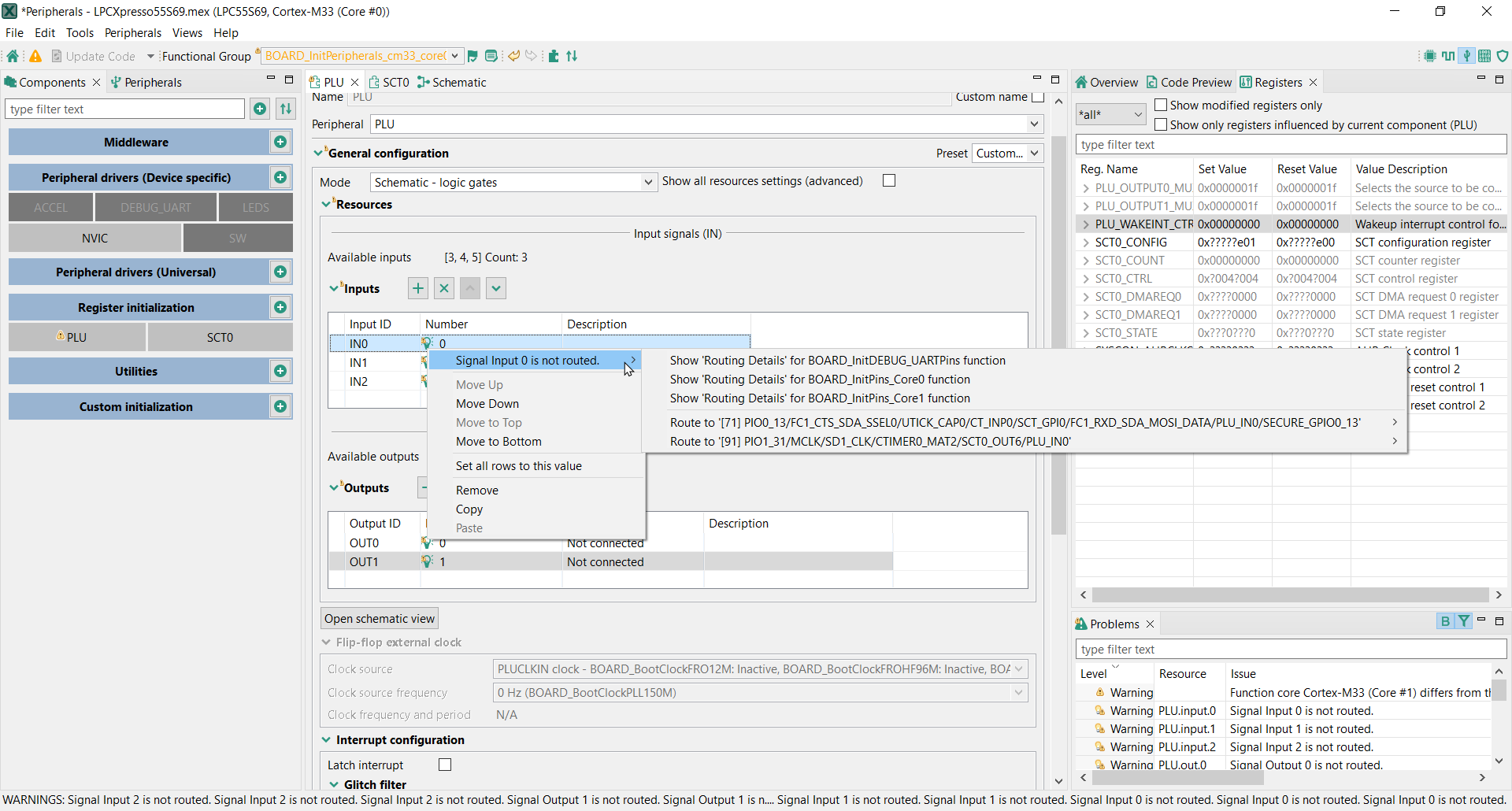

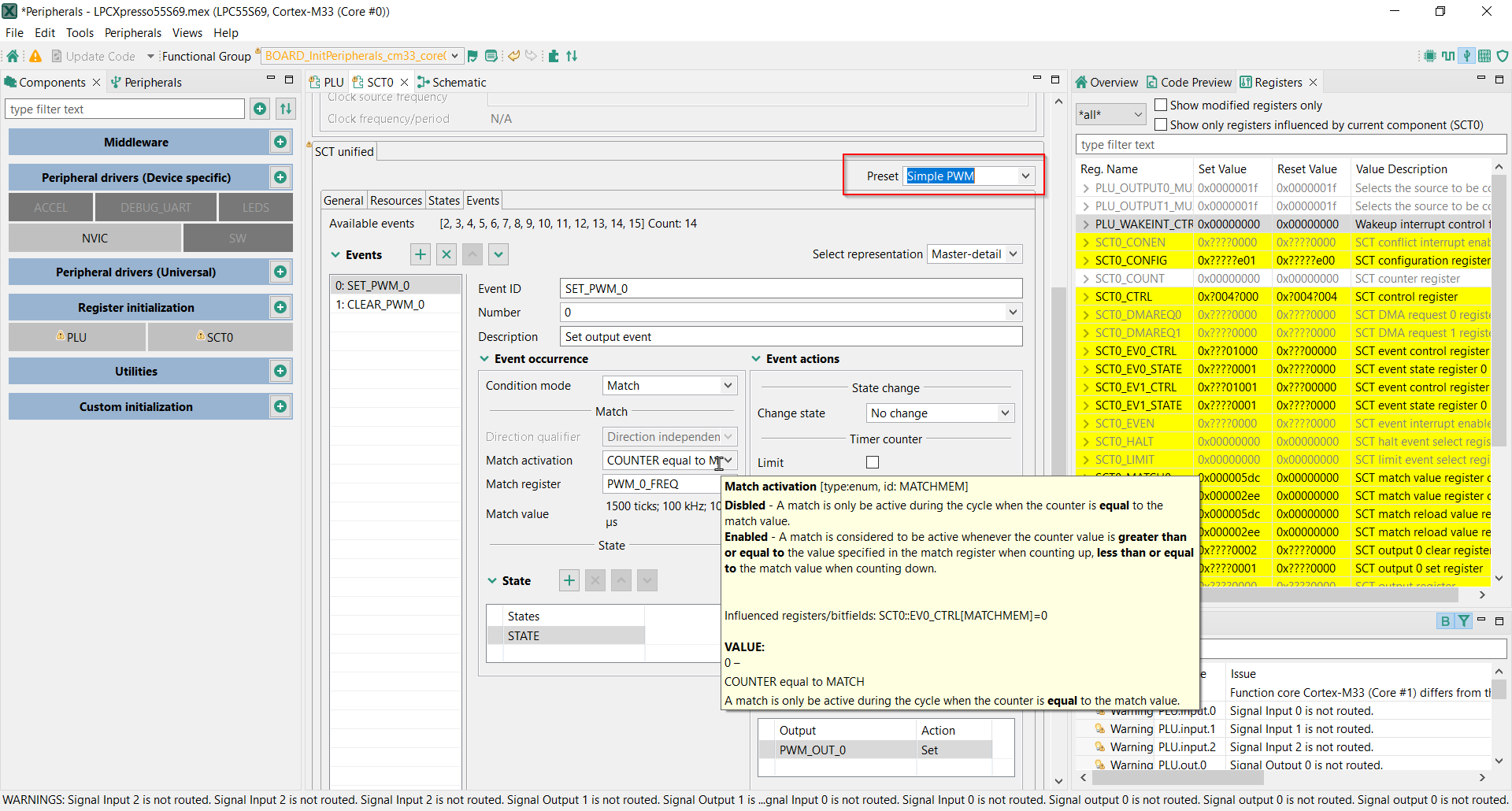

The LPC804 MCU and several devices in the LPC5500 and MCX N series incorporate a

Programmable Logic unit (PLU) that can be used to implement a variety of

interfaces and/or glue logic functions, reducing system component count

and often greatly reducing processing load on the MCU itself. Logic

designs for the

PLU

can be created and validated using the PLU Register Initialization

Component in the peripherals tool from the MCUXpresso configuration tools

suite.

Devices with the PLU feature are shown below. Note that the SDK support

for these boards can also be downloaded from within MCUXpresso IDE.

Coprocessors

Arm Cortex-M33 Coprocessor

The Armv8-M architecture includes support for coprocessor extensions, and

NXP has used this capability to develop highly efficient extensions for

DSP and security-related processing.

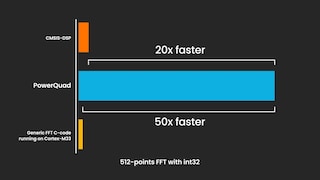

PowerQuad Coprocessor

PowerQuad is a coprocessor designed by NXP to improve energy efficiency

and performance when implementing DSP algorithms using its MCUs based on

Cortex-M33 core. PowerQuad can be programmed directly or via an API that

is compatible with Arm’s CMSIS-DSP library. MCUXpresso SDK includes API

header files to support CMSIS-DSP, plus several examples showing their

use.

Supported CMSIS-DSP API calls include:

-

Matrix functions

- arm_mat_add_q15, arm_mat_add_q31, arm_mat_add_f32

- arm_mat_sub_q15, arm_mat_sub_q31, arm_mat_sub_f32

- arm_mat_mult_q15, arm_mat_mult_q31, arm_mat_mult_f32

- arm_mat_inverse_f32

- arm_mat_trans_q15, arm_mat_trans_q31, arm_mat_trans_f32

- arm_mat_scale_q15, arm_mat_scale_q31, arm_mat_scale_f32

-

Math functions

- arm_sqrt_q15, arm_sqrt_q31

- arm_sin_q15, arm_sin_q31, arm_sin_f32

- arm_cos_q15, arm_cos_q31, arm_cos_f32

-

Filter functions

- arm_fir_q15, arm_fir_q31, arm_fir_f32

- arm_conv_q15, arm_conv_q31, arm_conv_f32

- arm_correlate_q15, arm_correlate_q31, arm_correlate_f32

-

Transform functions

- arm_rfft_q15, arm_rfft_q31

- arm_cfft_q15, arm_cfft_q31

- arm_ifft_q15, arm_ifft_q31

- arm_dct4_q15, arm_dct4_q31

PowerQuad has other hardware capabilities, such as transcendental

functions, and examples of using these are also provided in the SDK.

Devices with PowerQuad are shown below. Note that the SDK support for

these boards can also be downloaded from within MCUXpresso IDE.

|

| Device Family |

Cores |

Recommended Evaluation Boards

|

| LPC55S6x |

Dual Cortex-M33 |

LPCXpresso55S69

|

| i.MX RT685 |

Cortex-M33 and Cadence® Tensilica® HiFi 4 DSP

|

MIMXRT685-EVK

|

CASPER

To address the challenges of asymmetric cryptography, NXP has developed

CASPER, a Cryptographic Accelerator and Signaling Processing Engine with

RAM-sharing. It is a hardware accelerator engine for certain asymmetric

cryptographic algorithms, such as Elliptic Curve Cryptography (ECC).

CASPER sits on the Cortex-M33 coprocessor buses. CASPER is utilized by

NXP’s implementation of MbedTLS in MCUXpresso SDK, so you can take

advantage of the speed and energy-saving benefits with no additional

effort compared to a software-only approach.

Devices with CASPER are shown below. Note that the SDK support for these

boards can also be downloaded from within MCUXpresso IDE.

|

| Device Family |

Cores |

Recommended Evaluation Boards

|

| LPC55S6x |

Dual Cortex-M33 |

LPCXpresso55S69

|

| i.MX RT685 |

Cortex-M33 and Cadence Tensilica HiFi 4 DSP |

MIMXRT685-EVK

|

Specialized Interfaces

NXP microcontrollers include powerful, innovative interface peripherals to

reduce system cost, improve energy consumption and leave more processor

cycles for your application.

Interface Block

LPC5500 series MCUs incorporate a specialized, programmable peripheral

block that can be used to implement a variety of interfaces with little or

zero overhead for the Arm cores they contain, enabling you to implement

lower system cost implementations, save energy and leave more processing

cycles for your applications. NXP provides drivers and examples for some

specialized peripherals (upon request) that can be used with MCUXpresso

SDK projects.

Devices with this specialized peripheral block feature are shown below.

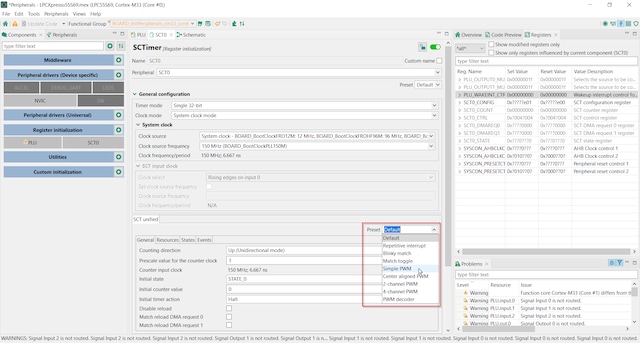

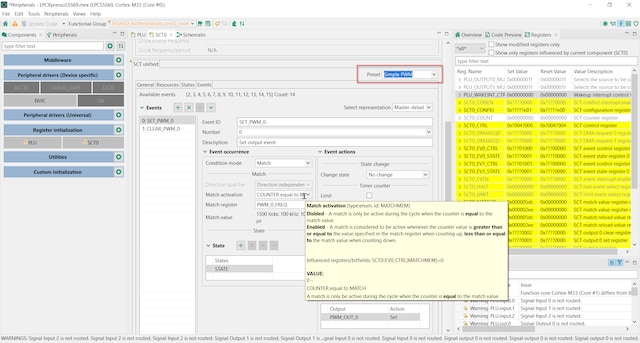

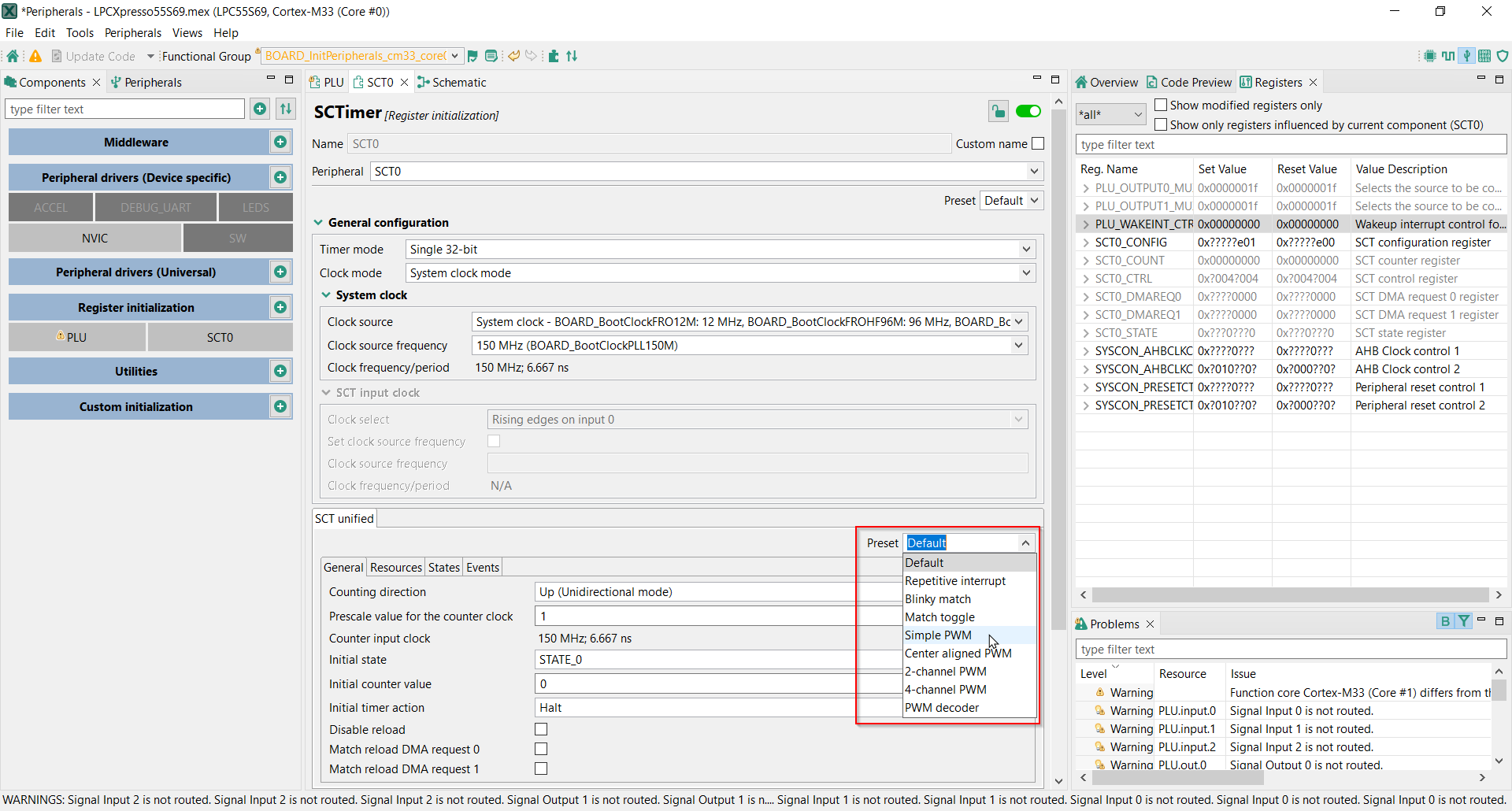

State-controlled Timers

Several MCUs in NXP’s portfolio include powerful peripherals that can

solve many logic and timing challenges.

The State Configurable Timer (SCT) is available on most LPC and i.MX RT600

microcontrollers. At its core, the SCT is a up/down counter that can be

sequenced with up to 16 events on LPC5500 series devices (the number of

events supported varies with the device family). The events can be

triggered by IO or by one of 16 possible counter matches. An event can

then update a state variable, generate IO activity (set, clear, toggle) or

start/stop/reverse the counter. In some cases, the SCT can be used to

build a semiautonomous subsystem, with very low MCU overhead to manage it.

Using these capabilities, a broad range of sophisticated system designs

can be implemented, often achieving system cost savings by reducing the

need for external FPGAs or other components. MCUXpresso SDK includes

examples of PWM timer implementations using the SCT, and the MCUXpresso

Peripheral Configuration Tool enables design of state machine-controlled

timers on-the-fly.

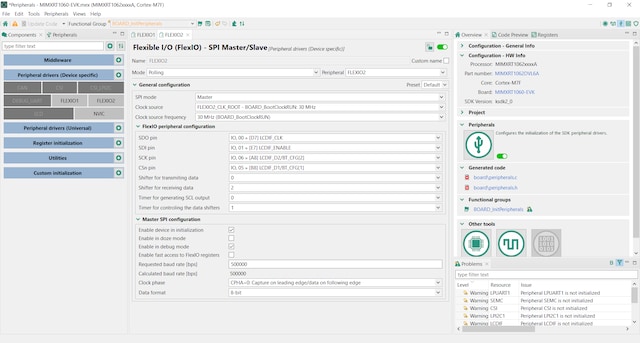

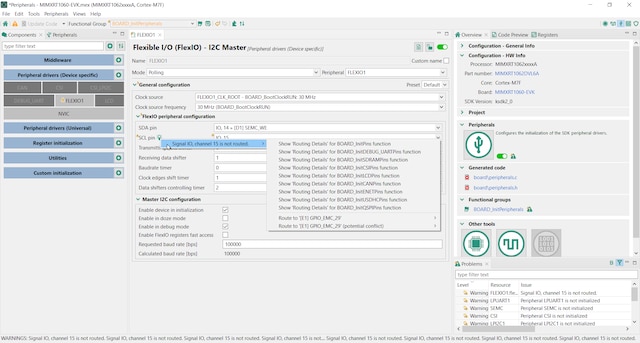

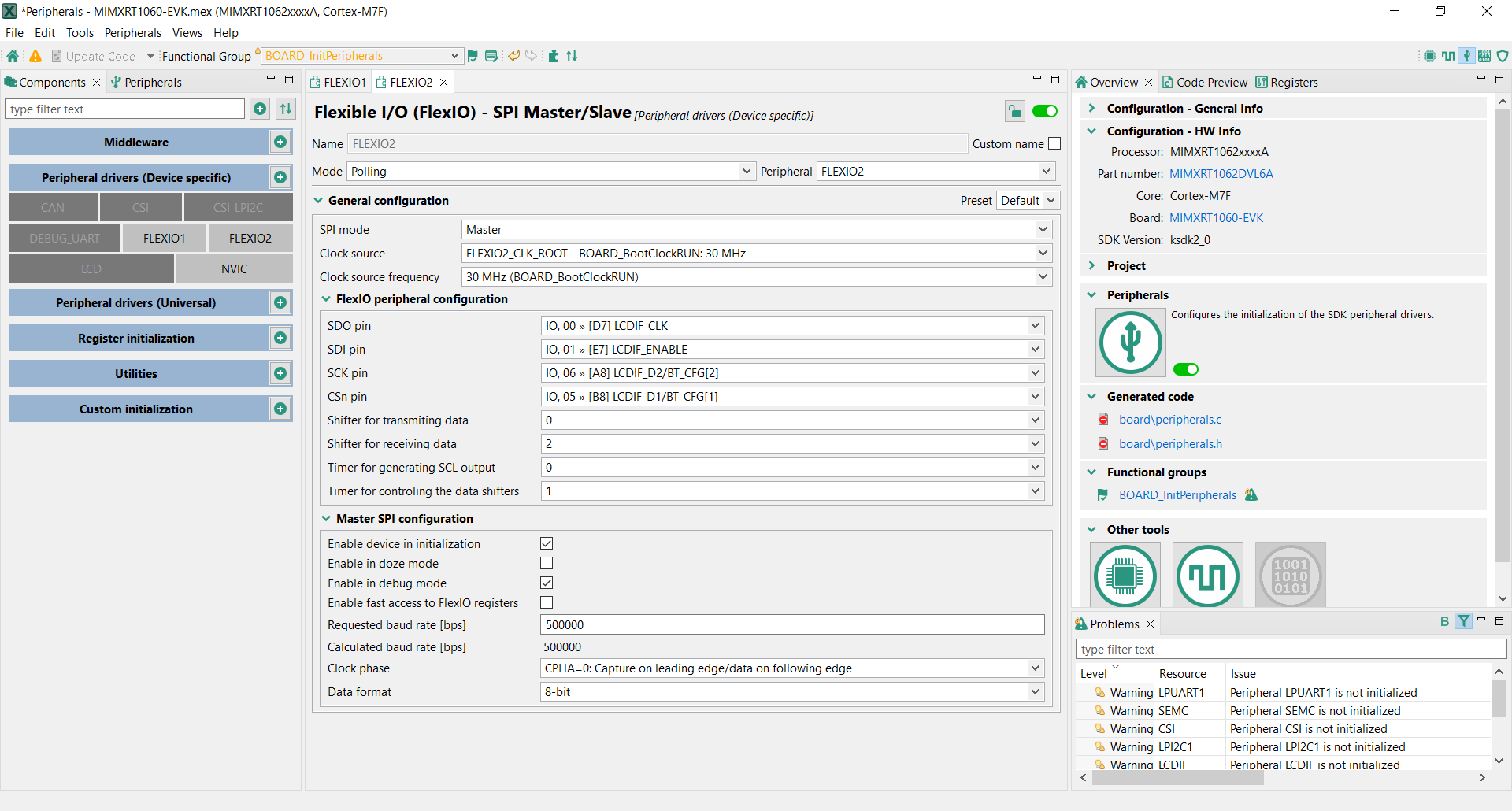

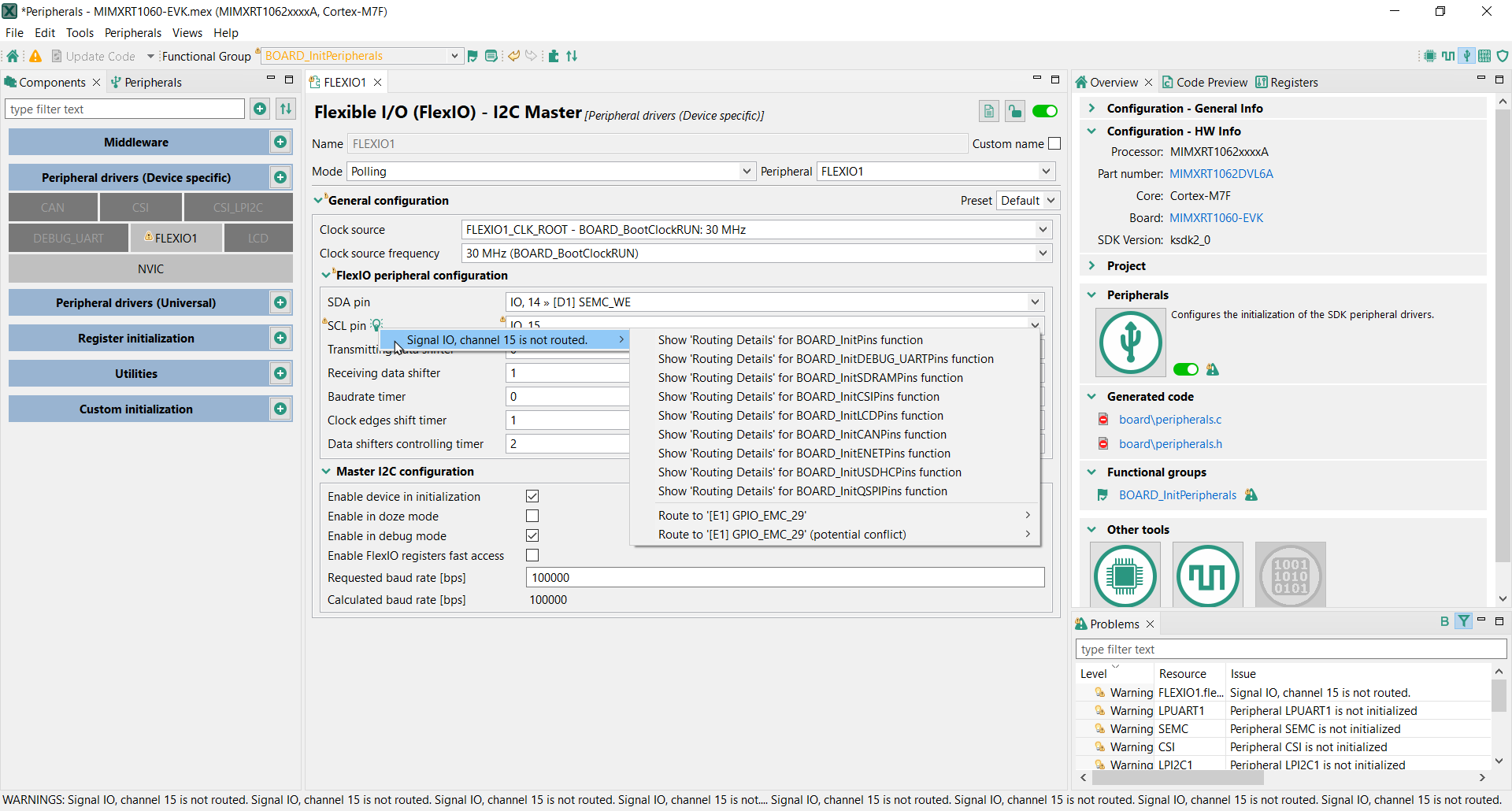

FlexIO Module

The FlexIO module is available in several members of the K32, Kinetis,

i.MX RT MCU families. The FlexIO module is very flexible, allowing you to

configure it according to your communication needs; it is capable of

emulating various serial communication protocols such as UART, SPI and

I²C. The main components of the FlexIO module are the shifters,

timers and pins; data is loaded onto a shifter and a timer is assigned to

generate the shifter clock and use a pin to input/output the data to/from

the shifter. Shifters have a timer assigned to them to generate the shift

clock and it can be configured to shift data in or out. Beyond serial

interfaces, FlexIO can also emulate parallel interfaces, such as LCD

display drivers, with very low MCU overheard. Examples using FlexIO to

emulate I²C, I²S, UART, SPI and displays that match

the 8080 and 6800 bus protocols are included in MCUXpresso SDK and

Peripheral configuration tools, along with PWM driver examples. Examples

for camera interfaces and IrDA camera interfaces are available in

application notes from the NXP website by searching for “FlexIO

application note”.

The table below shows which devices include the SCT and/or FlexIO special

peripherals.

|

| Device Family |

Cores |

FlexIO |

SCT |

| K8x, K27/28 |

Cortex-M4 |

|

- |

| KE1xx |

Cortex-M4/M0+ / Cortex-M0+ |

|

- |

| KL (excl. KL0x) |

Cortex-M0+ |

|

- |

| K32 L |

Cortex-M4/M0+ / Cortex-M0+ |

|

- |

| i.MX RT1010 |

Cortex-M7 |

|

- |

| i.MX RT1020 |

Cortex-M7 |

|

- |

| i.MX RT1050 |

Cortex-M7 |

|

- |

| i.MX RT1060 |

Cortex-M7 |

|

- |

| i.MX RT1160 |

Cortex-M7 / Cortex-M4 |

|

- |

| i.MX RT1170 |

Cortex-M7 / Cortex-M4 |

|

- |

| LPC81x/82x/83/x84x |

Cortex-M0 / M0+ |

- |

|

| LPC51U68 |

Cortex-M0+ |

- |

|

| LPC54000 |

Cortex-M4 |

- |

|

| LPC5500 |

Cortex-M33 / Dual Cortex-M33 |

- |

|

| i.MX RT500 |

Cortex-M33 / Cadence Tensilica Fusion F1 DSP |

|

|

| i.MX RT600 |

Cortex-M33 / Cadence Tensilica HiFi 4 DSP |

- |

|

| MCX N23x |

Cortex-M33 |

|

- |

| MCX N94x/54x |

Cortex-M33 |

|

|

| MCX W71x |

Cortex-M33 |

|

|

| MCX W72x |

Cortex-M33 |

|

|

FlexPWM Module

The Flex Pulse Width Modulator (FlexPWM) module is an advanced component designed for precise motor control. It features multiple PWM submodules used for driving multi-phase motors. The FlexPWM module can generate a variety of switching patterns, including highly sophisticated waveforms, making it ideal for detailed motor control applications. This functionality ensures efficient and smooth operation in complex motor-driven systems, providing the necessary control and precision required for optimal performance.

For more information on motor control applications leveraging (not only) FlexPWM please visit Motor Control SDK page.