Safe Assure® (Functional Safety)

When it comes to functional safety, NXP stands for quality and reliability. Our SafeAssure program simplifies system-level safety requirements in accordance with ISO 26262.

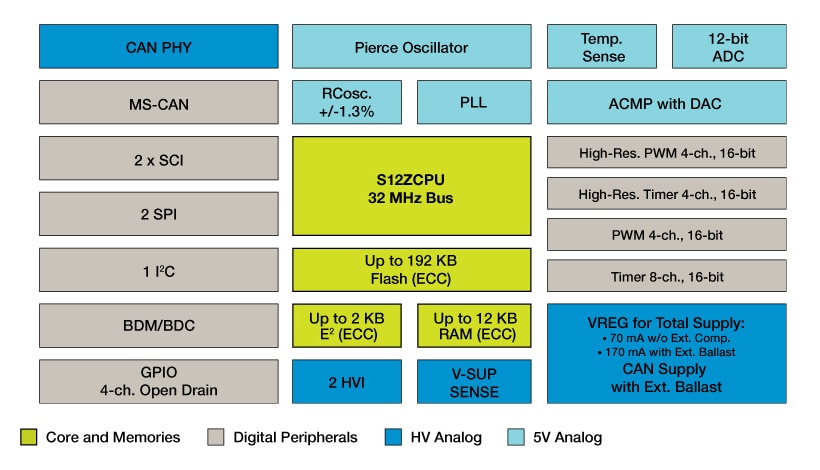

The S12ZVC platform, part of the S12 MagniV® mixed-signal MCU family, offers a low-cost, highly integrated solution that enables the design of smallest possible automotive CAN-termination nodes, while the family concept gives you scalability for platform design.

The S12ZVC integrates a sophisticated S12Z core together with a 12 V to 5 V voltage regulator and a CAN physical layer for automotive and industrial applications such as sensors, actuators switch panels or other user interfaces.

For additional information and sample availability, contact your local NXP Sales Office.

Note: To see the product features close this window.

When it comes to functional safety, NXP stands for quality and reliability. Our SafeAssure program simplifies system-level safety requirements in accordance with ISO 26262.

Participating products are available for a minimum of 10 years. Designated participating products developed for the automotive, telecom and medical segments are available for a minimum of 15 years.

| Feature | S12ZVCA | S12ZVCA | S12ZVC | S12ZVC | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Package | 64-pin LQFP-EP | 48-pin LQFP | 64-pin LQFP-EP | 48-pin LQFP | ||||||||||||

| Flash memory (ECC) (KByte) | 192 | 128 | 96 | 64 | 192 | 128 | 96 | 64 | 192 | 128 | 96 | 64 | 192 | 128 | 96 | 64 |

| EEPROM (ECC) (KByte)

(4-byte erasable) |

2 | 2 | 2 | 1 | 2 | 2 | 2 | 1 | 2 | 2 | 2 | 1 | 2 | 2 | 2 | 1 |

| RAM (ECC) (KByte) | 12 | 8 | 8 | 4 | 12 | 8 | 8 | 4 | 12 | 8 | 8 | 4 | 12 | 8 | 8 | 4 |

| High Speed CAN Physical Layer | 1 | 1 | 1 | 1 | ||||||||||||

| High Voltage Inputs | 2 | 2 | 2 | 2 | ||||||||||||

| Vreg for CAN PHY with ext. ballast

(BCTLC) |

yes | yes | yes | yes | ||||||||||||

| VDDX/VSSX pins | 2/2 | 2/2 | 2/2 | 2/2 | ||||||||||||

| msCAN | 1 | 1 | 1 | 1 | ||||||||||||

| SCI/SPI/IIC | 2/2/1 | 2/1/1 | 2/2/1 | 2/1/1 | ||||||||||||

| SENT (Transmitter) | 1 | 1 | 1 | 1 | ||||||||||||

| 16-bit Timer channels | 8 + 4 (20 ns resolution) | 4 + 4 (20 ns resolution) | 8 + 4 (20 ns resolution) | 4 + 4 (20 ns resolution) | ||||||||||||

| 16-bit PWM channels | 4 + 4 (20 ns resolution) | 4 + 3 (20 ns resolution) | 4 + 4 (20 ns resolution) | 4 + 3 (20 ns resolution) | ||||||||||||

| ADC channels | 16 (12-bit) | 10 (12-bit) | 16 (10-bit) | 10 (10-bit) | ||||||||||||

| 8-bit DAC | 1 | 1 | - | - | ||||||||||||

| ACMP 5V (with rail-to-rail inputs) | 2 | 2 | - | - | ||||||||||||

| EVDD (20 mA source) | 1 | 1 | 1 | 1 | ||||||||||||

| N-GPIO (25 mA sink) | 4 | 4 | 4 | 4 | ||||||||||||

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Quick reference to our documentation types

1-10 of 35 documents

Compact List

Please wait while your secure files are loading.

2 design files

Receive the full breakdown. See the product footprint and more in the eCad file.

Please wait while your secure files are loading.

1-5 of 6 hardware offerings

Additional hardware available. View our featured partner solutions.

4 hardware offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

Quick reference to our software types.

1-5 of 13 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

4 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

3 engineering services

.svg?imwidth=300)

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

4 trainings