- Products

- Processors and Microcontrollers

- Arm Microcontrollers

- General Purpose MCUs

- MCX Arm Cortex-M

- K32 L Series Arm Cortex-M4/M0+

- K Series Arm Cortex-M4

- KL Series Arm Cortex-M0+

- KV Series Arm Cortex-M4/M0+/M7

- KE Series Arm Cortex-M4/M0+

- KM Series Arm Cortex-M0+

- LPC800 Arm Cortex-M0+

- LPC1100 Arm Cortex-M0+/M0

- LPC1200 Arm Cortex-M0

- LPC1300 Arm Cortex-M3

- LPC1500 Arm Cortex-M3

- LPC1700 Arm Cortex-M3

- LPC1800 Arm Cortex-M3

- LPC4000 Arm Cortex-M4

- LPC4300 Arm Cortex-M4/M0

- LPC51U68 Arm Cortex-M0+

- LPC54000 Arm Cortex-M4

- LPC5500 Arm Cortex-M33

- LPC2000 Arm7

- LPC3000 Arm9

- Developer Resources

- i.MX RT Crossover MCUs

- Automotive MCUs

- General Purpose MCUs

- Arm Processors

- S32 Automotive Platform

- Power Architecture

- Additional MPU/MCUs Architectures

- Legacy MPU/MCUs

- Arm Microcontrollers

- Analog and Mixed Signal

- Audio

- Battery Management

- Interfaces

- Power Drivers

- Power Management

- Radio

- Radio Frequency (RF)

- RFID / NFC

- Security and Authentication

- Sensors

- Wireless Connectivity

- Product Finders

- NXP Product Information

- Design Advisor

- Processors and Microcontrollers

MCX Industrial and IoT Microcontrollers

NXP MCX Microcontrollers (MCUs) are a diverse group of Arm® Cortex®-M MCUs that offer simplified system design. MCX Microcontrollers are optimized for use cases that demand and expanded selection of peripherals and memory options. MCX MCUs bring a developer-focused experience using our MCUXpresso suite of software and tools.

Scalable MCX Portfolio

| Family | Series Overview | Highlights |

|---|---|---|

|

MCX A |

|

|

|

MCX N |

|

|

|

MCX C |

|

|

|

MCX L |

|

|

|

MCX E |

|

|

|

MCX W |

|

|

Design Resources

Design Without Bounds

MCX MCUs deliver scalable, high-performance solutions for AI/ML, motor control and industrial automation.

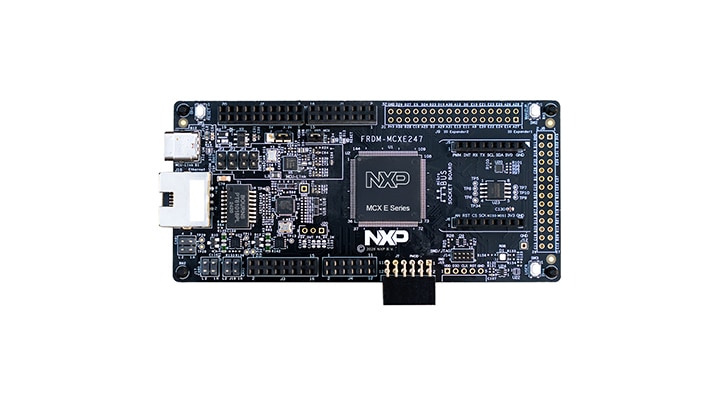

Latest Development Boards

Compact and scalable. Unlock the possibilities with the extensive ecosystem that come along the latest FRDM development boards.

MCX E Series – Scalable MCX designed for robust, reliable and safe operation in industrial, automation, transport, medical, and communication systems.

The FRDM-MCXW23 is a development board featuring MCX W23 Bluetooth Low Energy (LE) MCU, designed for applications such as portable medical devices, home appliance and automation and asset tracking.

FRDM-MCXA346 is a compact and scalable development board for rapid prototyping of FRDM-MCXA346 microcontroller units (MCUs).

FAQs

What are NXP MCX microcontrollers and what makes them unique?

NXP MCX microcontrollers are a scalable portfolio of Arm® Cortex®-M-based MCUs designed to simplify edge device development. They stand out for their integration of AI/ML capabilities, ultralow power consumption, advanced security features and support for wireless connectivity like Bluetooth and Matter.

Which applications are MCX microcontrollers best suited for?

MCX MCUs are ideal for a wide range of applications including smart home devices, industrial automation, motor control, secure access systems, metering and edge AI. Their versatility makes them suitable for both consumer and industrial-grade solutions.

How do MCX microcontrollers support AI and machine learning at the edge?

MCX MCUs feature the eIQ® Neutron Neural Processing Unit (NPU), enabling efficient TinyML inference for tasks like anomaly detection, object classification and voice recognition. This allows developers to deploy intelligent features on resource-constrained devices.

What security features are built into MCX microcontrollers?

MCX MCUs are designed with security in mind, offering features like EdgeLock® Secure Enclave, TrustZone®, authenticated boot and support for certifications such as SESIP3, PSA Level 3 and FIPS 140-3. These features help ensure device integrity and compliance with industry standards.

How do MCX microcontrollers help reduce power consumption in always-on devices?

With patented Adaptive Dynamic Voltage Control (ADVC) and ultralow power modes (as low as 0.4 µA with RAM retention), MCX MCUs are optimized for always-on, always-sensing applications. This makes them ideal for battery-powered and energy-efficient designs.

What tools and resources are available for developing with MCX microcontrollers?

NXP provides the MCUXpresso Developer Experience, including SDKs, IDEs like Visual Studio Code, FreeMASTER for real-time debugging, and support for Zephyr™ and FreeRTOS. Developers can also access application examples, expansion boards and secure provisioning tools to accelerate.

MCX A Series Just Doubled

Six new families push the MCX A series further, expanding scalable performance, security and connectivity for Industrial and IoT designs.

Documentation

|

Scalable, high performance, general-purpose Arm® Cortex®-M based MCUs. |

Factsheet | Jul 1, 2025 | Rev 1.0 |