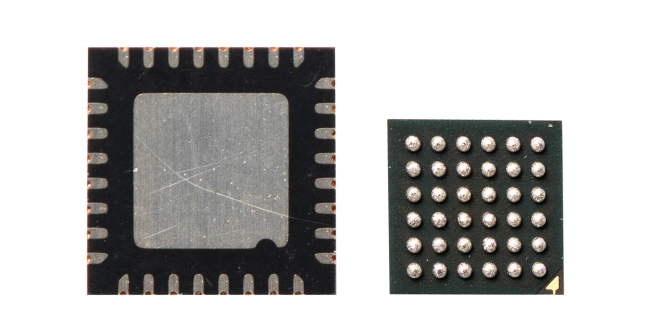

MIFARE SAM AV3

As the next generation of NXP’s MIFARE Plus product family, the MIFARE Plus EV2 IC is designed to be both a gateway for new Smart City applications and a compelling upgrade, in terms of security and connectivity, for existing deployments. Its expanded feature set makes it a great choice for contactless Smart City services:

Part numbers include: MF1P2200DA4, MF1P2200DA8, MF1P2201DUD, MF1P2230DA4, MF1P2230DA8, MF1P2231DUD, MF1P4200DA4, MF1P4200DA8, MF1P4201DUD, MF1P4230DA4, MF1P4230DA8, MF1P4231DUD, MF1PH2200DA4, MF1PH2200DA8, MF1PH2201DUD, MF1PH2230DA4, MF1PH2230DA8, MF1PH2231DUD, MF1PH4200DA4, MF1PH4200DA8, MF1PH4201DUD, MF1PH4230DA4, MF1PH4230DA8, MF1PH4231DUD.

| Memory | MIFARE Plus EV2 | MIFARE Plus X |

|---|---|---|

| Memory configuration | Block/sector structure | Block/sector structure |

| Memory size | 2 kB / 4 kB | 2 kB / 4 kB |

| ISO/IEC | ISO/IEC 14443 A 1-4 ISO/IEC 7816 |

ISO/IEC 14443 A 1-4 ISO/IEC 7816 |

| UID/ONUID | 7B UID or 4 B ONUID | 7B UID or 4 B ONUID |

| Data rates | Up to 848 kbps according to ISO/IEC 14443-4 | Up to 848 kbps according to ISO/IEC 14443-4 |

| Algorithm | AES 128-bit, secure messaging, legacy Crypto1 | AES 128-bit, secure messaging, legacy Crypto1 |

| Security Level concept | Sector-by-Sector or card | Card only |

| SL1SL3MixMode | Secure backend connection into SL1 sectors | - |

| Transaction MAC (TMAC) | Secure validation of back-end transaction | - |

| Transaction Timer | Mitigate man-in-the-middle attacks | - |

| Common Criteria certification | EAL5+ for IC HW and SW | EAL4+ for IC HW and SW |

MIFARE SAM AV3

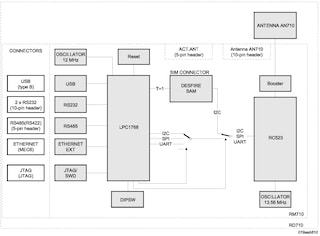

CLRC663 plus Family: High-Performance NFC Frontends

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Quick reference to our documentation types.

1-5 of 11 documents

Please wait while your secure files are loading.

Receive the full breakdown. See the product footprint and more in the eCad file.

Receive the full breakdown. See the product footprint and more in the eCad file.

2 hardware offerings

3 hardware offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

Quick reference to our software types.

2 software files

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

1 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

1 engineering service

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

3 trainings