Application Note (15)

-

Understanding SYSCLK Jitter[AN4056]

-

PowerQUICC™ Data Cache Coherency[AN3544]

-

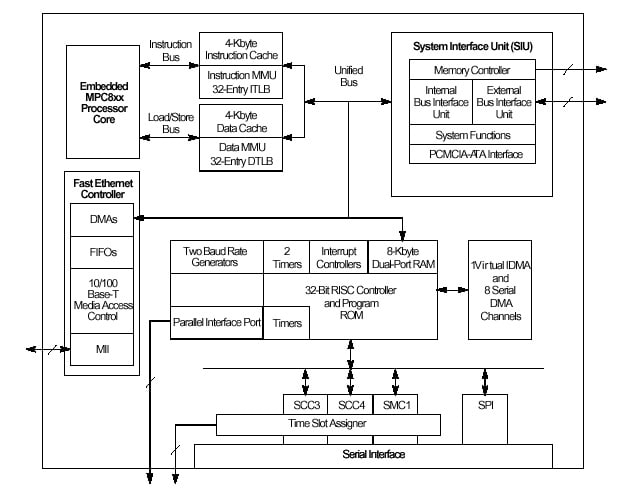

Designing with the MPC852T[AN2568]

Application Note Software (5)

Data Sheet (3)

-

MPC852T Hardware Specifications[MPC852TEC]

-

MPC853T Hardware Specification[MPC853TEC]

-

MPC852T PowerQUICC® Technical Summary[MPC852TTS]

Errata (1)

-

Device Errata for the MPC866 Family[MPC866CE]

Fact Sheet (2)

-

USB-ML-PPCBDM Fact Sheet[USBMLPPCBDMFS]

-

MPC852T PowerQUICC® Fact Sheet[MPC852TFS]

Package Information (2)

-

PBGA Packaging Customer Tutorial[PBGAPRES]

-

MPC852T Pb-Free Packaging Information[MPC852TPKG]

Reference Manual (3)

-

MPC8xx Digital Signal Processing Addendum[MPC8XXRMAD]