Application Note (3)

Data Sheet (1)

Package Information (1)

Packing Information (1)

User Guide (2)

-

PCA9632 demonstration board OM13269[UM10528]

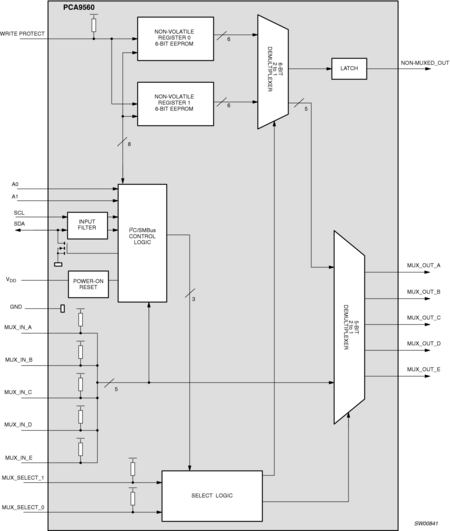

The PCA9560 is a 20-pin CMOS device consisting of two 6-bit non-volatile EEPROM registers, 5 hardware pin inputs and a 5-bit multiplexed output with one latched EEPROM bit. It is used for DIP switch-free or jumper-less system configuration and supports Mobile and Desktop VID Configuration, where 3 preset values (2 sets of internal non-volatile registers and 1 set of external hardware pins) set processor voltage for operation in either performance, deep sleep or deeper sleep modes. The PCA9560 is also useful in server and telecom/networking applications when used to replace DIP switches or jumpers, since the settings can be easily changed via I²C/SMBus without having to power down the equipment to open the cabinet. The non-volatile memory retains the most current setting selected before the power is turned off.

The PCA9560 typically resides between the CPU and Voltage Regulator Module (VRM) when used for CPU VID (Voltage IDentification code) configuration. It is used to bypass the CPU-defined VID values and provide a different set of VID values to the VRM, if an increase in the CPU voltage is desired. An increase in CPU voltage combined with an increase in CPU frequency leads to a performance boost of up to 7.5pct. Lower CPU voltage reduces power consumption. The main advantage of the PCA9560 over the older PCA9559 device in this application is that it contains two internal non-volatile EEPROM registers instead of just one, allowing three independent settings (performance operation, deep sleep mode and deeper sleep mode) instead of only two (performance operation and deep sleep mode). The PCA9560 is footprint compatible and a drop-in replacement for the PCA9559, without any software modifications required.

The PCA9560 has 2 address pins allow up to 4 devices to be placed on the same I²C bus or SMBus.

Choose a diagram:

Note: To see the product features close this window.

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Quick reference to our documentation types

8 documents

Compact List

Please wait while your secure files are loading.

2 design files

Receive the full breakdown. See the product footprint and more in the eCad file.

Please wait while your secure files are loading.

2 engineering services

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.