Safe Assure® (Functional Safety)

When it comes to functional safety, NXP stands for quality and reliability. Our SafeAssure program simplifies system-level safety requirements in accordance with ISO 26262.

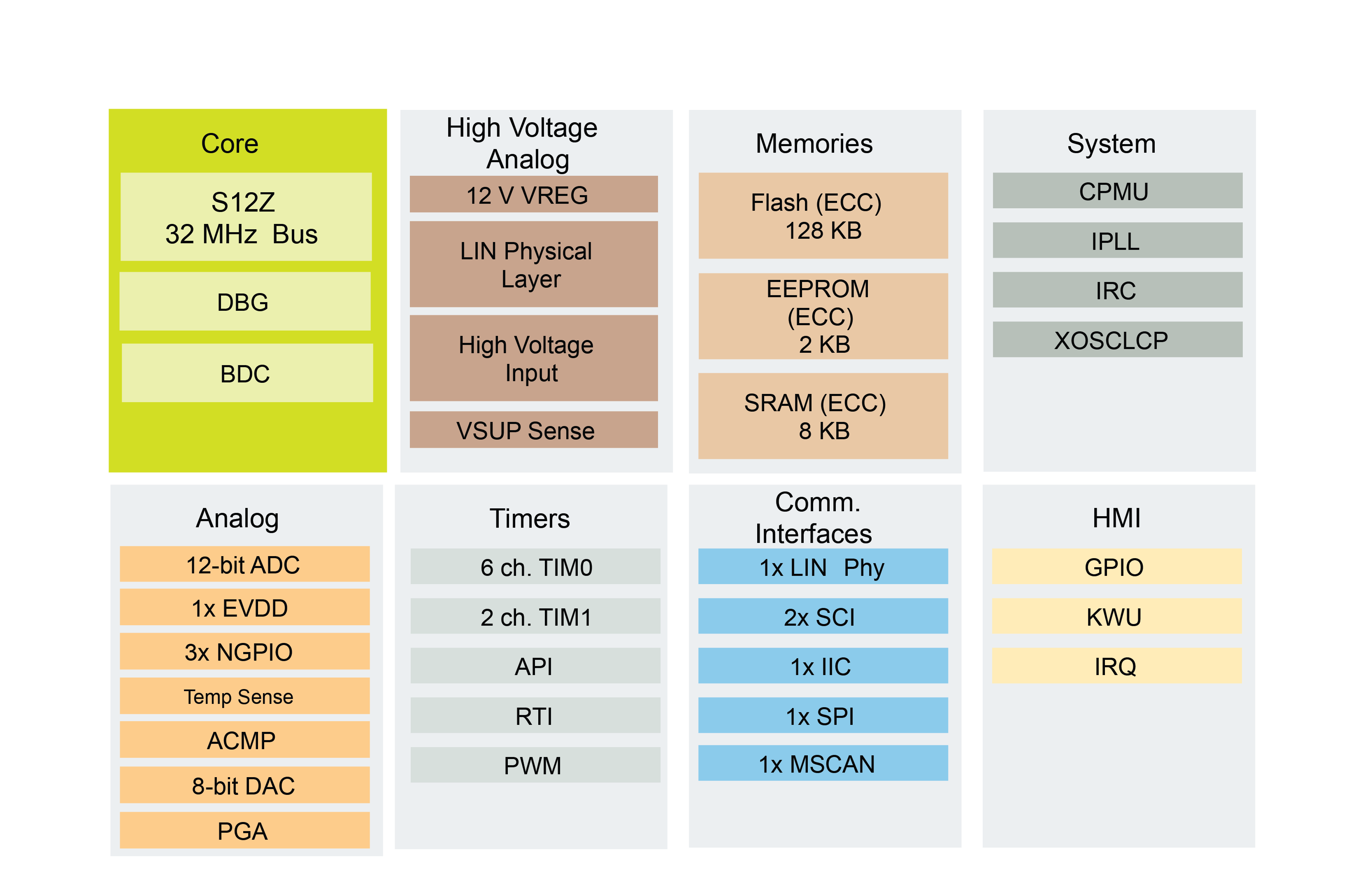

The S12ZVL platform, part of the S12 MagniV mixed-signal MCU product line, offers a low-cost, highly integrated solution for space-constrained automotive LIN nodes. With memory sizes from 8-128K flash, the family provides scalability for platform standardization.

The S12ZVL integrates a sophisticated S12Z core with a 12 V to 5 V voltage regulator and a LIN physical layer transceiver for automotive and industrial applications such as sensor interfaces, actuators, switch panels or ambient lighting.

Note: To see the product features close this window.

When it comes to functional safety, NXP stands for quality and reliability. Our SafeAssure program simplifies system-level safety requirements in accordance with ISO 26262.

Participating products are available for a minimum of 10 years. Designated participating products developed for the automotive, telecom and medical segments are available for a minimum of 15 years.

| 48-LQFP | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| S12ZVLA | S12ZVL | S12ZVL | ||||||||

| Memory | Flash [kB] | 128 | 96 | 64 | 128 | 96 | 64 | 32 | 16 | 8 |

| EEPROM [kB] | 2 | 1 | 2 | 1 | 0.128 | |||||

| RAM [kB] | 8 | 4 | 8 | 4 | 1 | 0.5 | ||||

| UHV | V reg | 5V / 3.3V ; 70mA or up to 170 (with ballast option / BCTL) |

5V; 70mA or up to 170 (with ballast option / BCTL) |

|||||||

| V reg tolerance | 2% | 3% | 3% | |||||||

| PHY | LIN | |||||||||

| HVI | 1 | |||||||||

| Analog | ADC (LB) channel | 10 | ||||||||

| ADC (LB) resolution | 12 Bit | 10 Bit | 10 Bit | |||||||

| ACMP with 8bit DAC | 1 | - | - | |||||||

| PGA | 1 | - | - | |||||||

| PGA levels | 10/20/40/80x | - | - | |||||||

| Comms | SCI | 2 | ||||||||

| SPI | 1 | |||||||||

| IIC | 1 | |||||||||

| MSCAN | 1 | - | ||||||||

| Tim | Timer (6+2ch) | 6ch + 2ch (16 Bit) | ||||||||

| PWM | 8ch 8Bit (or 4ch 16Bit) | |||||||||

| I/O | GPIO | 35 | - | |||||||

| intrr. Cap. IO (5/12v) | 22/1 | |||||||||

| eVdd (5V/20mA) | 1 | |||||||||

| N-GPIOs (5V / 25mA) | 3 | 1 | ||||||||

| Temperature options | C / V / M | C / V / M | ||||||||

| 32-LQFP | 32-QFN | 32-LQFP | 32-QFN | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S12ZVLA | S12ZVL | S12ZVLA | S12ZVL | S12ZVLS | |||||||||||

| Memory | Flash [kB] | 128 | 96 | 64 | 128 | 96 | 64 | 128 | 96 | 64 | 32 | 16 | 8 | 32 | 16 |

| EEPROM [kB] | 2 | 1 | 2 | 1 | 2 | 1 | 0.128 | ||||||||

| RAM [kB] | 8 | 4 | 8 | 4 | 8 | 4 | 1 | 0.5 | 1 | ||||||

| UHV | V reg | 5V / 3.3V ; 70mA or up to 170 (with ballast option / BCTL) |

5V; 70mA or up to 170 (with ballast option / BCTL) |

||||||||||||

| V reg tolerance | 2% | 3% | 2% | 3% | |||||||||||

| PHY | LIN | ||||||||||||||

| HVI | 1 | ||||||||||||||

| Analog | ADC (LB) channel | 6 | 7 | 6 | |||||||||||

| ADC (LB) resolution | 12 Bit | 10 Bit | 12 Bit | 10 Bit | |||||||||||

| ACMP with 8bit DAC | 1 | 0 | 1 | - | |||||||||||

| PGA | 1 | - | 1 | - | |||||||||||

| PGA levels | 10/20/40/80x | - | 10/20/40/80x | - | |||||||||||

| Comms | SCI | 2 | |||||||||||||

| SPI | 1 | ||||||||||||||

| IIC | 1 | ||||||||||||||

| MSCAN | 1 | - | |||||||||||||

| Tim | Timer (6+2ch on silicon) | 6ch + 2ch (16 Bit) | |||||||||||||

| PWM | 8ch (16Bit) | 8ch 8Bit (or 4ch 16Bit) | |||||||||||||

| I/O | GPIO | 20 | |||||||||||||

| intrr. Cap. IO (5/12v) | 16/1 | ||||||||||||||

| eVdd (5V/20mA) | 1 | ||||||||||||||

| N-GPIOs (5V / 25mA) | 1 | 1 | 3 | ||||||||||||

| Temperature options | C / V / M | C / V / M | |||||||||||||

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Quick reference to our documentation types

1-10 of 37 documents

Compact List

Please wait while your secure files are loading.

4 design files

Please wait while your secure files are loading.

1-5 of 9 hardware offerings

Additional hardware available. View our featured partner solutions.

4 hardware offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

Quick reference to our software types.

1-5 of 12 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

4 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

3 engineering services

.svg?imwidth=300)

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.