The MPC8260 PowerQUICC® II™ is an advanced integrated communications processor designed for the telecommunications and networking markets.

The MPC8260 now offers floating point support.

The MPC8260 PowerQUICC II can best be described as the next generation MPC860 PowerQUICC®, providing higher performance in all areas of device operation, including greater flexibility, extended capabilities, and higher integration.

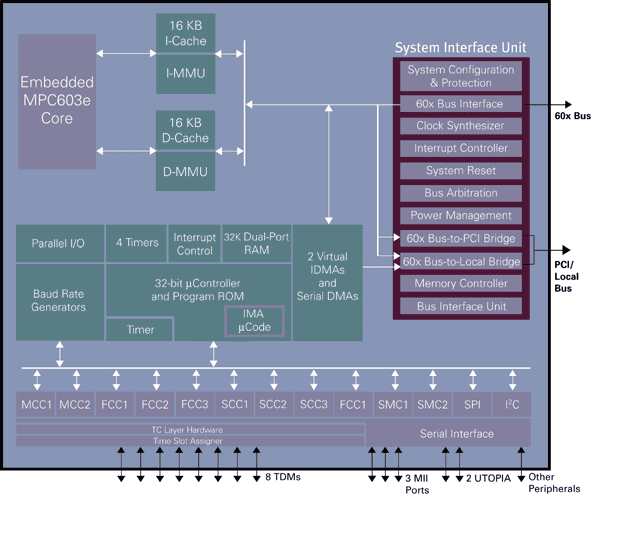

Like the MPC860, the MPC8260 integrates two main components, the embedded G2 core and the Communications Processor Module (CPM). This dual-processor architecture consumes less power than traditional architectures because the CPM offloads peripheral tasks from the embedded G2 core. The CPM simultaneously supports three fast serial communications controllers (FCCs), two multichannel controllers (MCCs), four serial communications controllers (SCCs), two serial management controllers (SMCs), one serial peripheral interface (SPI) and one I²C interface. The combination of the G2 core and the CPM, along with the versatility and performance of the MPC8260, provides customers with enormous potential in developing networking and communications products while significantly reducing time-to-market development stages.