Digital Signal Controller for Auto and Industrial Applications

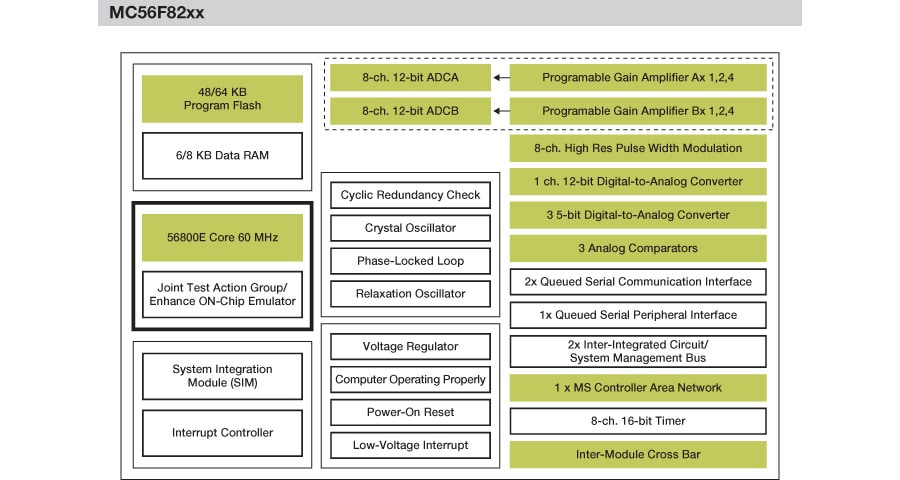

The NXP® MC56F825x/MC56F824x is a member of the 56800E core-based family of digital signal controllers (DSCs). It combines DSP processing power and microcontroller functionality on a single chip, with a flexible set of peripherals.

Note: To see the product features close this window.

Part numbers include: MC56F8245MLD, MC56F8245VLD, MC56F8246MLF, MC56F8246VLF, MC56F8247MLH, MC56F8247VLH, MC56F8255MLD, MC56F8255VLD, MC56F8256MLF, MC56F8256VLF, MC56F8257MLH, MC56F8257VLH.

Quick reference to our documentation types.

1-5 of 29 documents

Please wait while your secure files are loading.

1-5 of 7 hardware offerings

Additional hardware available. View our featured partner solutions.

3 hardware offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

Quick reference to our software types.

1-5 of 11 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

2 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

1 engineering service

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.