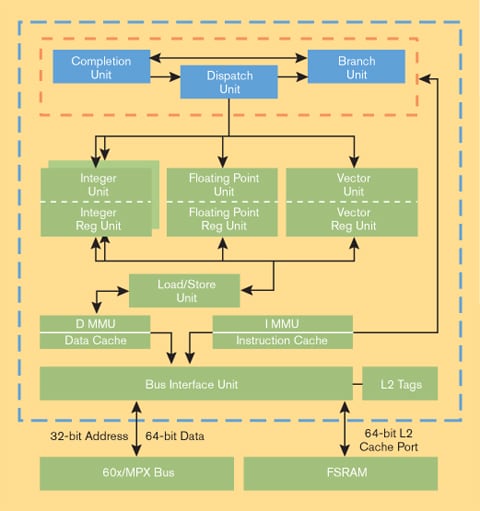

The MPC7410 Host Processor is a high-performance, low-power, 32-bit processor built on Power Architecture technology with a full 128-bit implementation of Our AltiVec®™ technology. This creates a microprocessor ideal for leading-edge computing, embedded network control, and signal processing applications. The MPC7410 offers the high-bandwidth MPX bus with minimized signal setup times and reduced idle cycles to increase maximum operating frequency to over 100 MHz, in addition to increased address and data bus bandwidth. To maintain compatibility for existing designs, the MPC7410 also supports the 60x bus protocol. MPC7410 microprocessors offer single-cycle double precision floating-point performance, full symmetric multi-procesing (SMP) capabilities, and support for up to 2MB of backside L2 cache. While the MPC7410 is software-compatible with existing MPC603e, MPC740, and MPC750 microprocessors, to utilize the full potential of the AltiVec technology changes to existing source code is required.