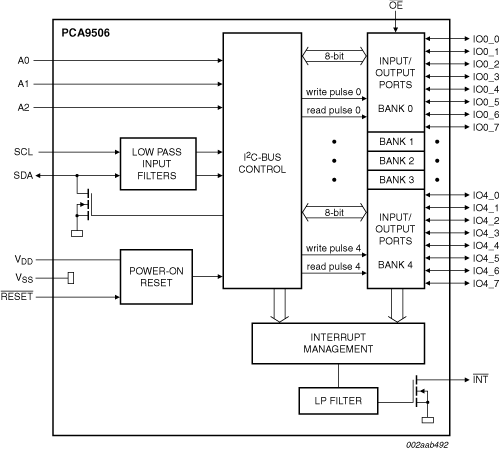

The PCA9505/PCA9506 provide 40-bit parallel input/output (I/O) port expansion for I²C-bus applications organized in 5 banks of 8 I/Os. At 5 V supply voltage, the outputs are capable of sourcing 10 mA and sinking 15 mA with a total package load of 600 mA to allow direct driving of 40 LEDs. Any of the 40 I/O ports can be configured as an input or output. Output ports are totem-pole and their logic state changes at the Acknowledge (bank change). The PCA9505 is identical to the PCA9506 except that it includes 100 kΩ internal pull-up resistors on all the I/Os. The PCA9506 does not include the internal pull-ups on the I/Os to reduce power consumption when used as outputs or when the input is driven by a push-pull driver.

The device can be configured to have each input port to be masked in order to prevent it from generating interrupts when its state changes and to have the I/O data logic state to be inverted when read by the system controller.

An open-drain interrupt (INT) output pin allows monitoring of the input pins and is asserted each time a change occurs in one or several input ports (unless masked).

The Output Enable (OE) pin 3-states any I/O selected as an output and can be used as an input signal to blink or dim LEDs (PWM with frequency > 80 Hz and change duty cycle).

The internal Power-On Reset (POR) or hardware reset (RESET) pin initializes the 40 I/Os as inputs. Three address select pins configure one of 8 target addresses.

The PCA9506 is available in 56-pin TSSOP and HVQFN packages, while the PCA9505 is available only in a TSSOP package. They are both specified over the -40 °C to +85 °C industrial temperature range.