Product Longevity

Participating products are available for a minimum of 10 years. Designated participating products developed for the automotive, telecom and medical segments are available for a minimum of 15 years.

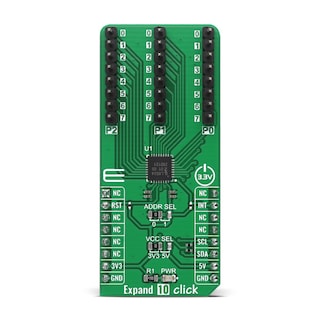

The PCAL6524 is a 24-bit general purpose I/O expander that provides remote I/O expansion for many microcontroller families via the Fast-mode Plus (Fm+) I²C-bus interface. The ultra-low-voltage interface allows for direct connection to a microcontroller operating down to 0.8 V.

NXP® I/O expanders provide a simple solution when additional I/Os are needed while keeping interconnections to a minimum, for example, in battery-powered mobile applications for interfacing to sensors, push buttons, keypad, etc. In addition to providing a flexible set of GPIOs, it simplifies interconnection of a processor running at one voltage level down to 0.8 V to I/O devices operating at a different voltage level 1.65 V to 5.5 V. The PCAL6524 has built-in level shifting feature that makes these devices extremely flexible in mixed power supply systems where communication between incompatible I/O voltages is required, allowing seamless communications with next-generation low voltage microprocessors and microcontrollers on the interface side (SDA/SCL) and peripherals at a higher voltage on the port side.

There are two supply voltages for PCAL6524: VDD(I2C-bus) and VDD(P). VDD(I2C-bus) provides the supply voltage for the interface at the controller side (for example, a microcontroller) and the VDD(P) provides the supply for core circuits and Port P. The bi-directional voltage level translation in the PCAL6524 is provided through VDD(I2C-bus). VDD(I2C-bus) should be connected to the VDD of the external SCL/SDA lines. This indicates the VDD level of the I²C-bus to the PCAL6524, while the voltage level on Port P of the PCAL6524 is determined by the VDD(P).

The PCAL6524 fully meets the Fm+ I²C-bus specification at speeds to 1 MHz and implements Agile I/O, which are additional features specifically designed to enhance the I/O. These additional features are programmable output drive strength, latchable inputs, programmable pull-up/pull-down resistors, maskable interrupt, interrupt status register, programmable open-drain or push-pull outputs.

Additional Agile I/O Plus features include I²C software reset and device ID. Interrupts can be specified by level or edge and can be cleared individually without disturbing the other interrupt events. Also, switch debounce hardware is implemented.

At power-on, the I/Os are configured as inputs. However, the system controller can enable the I/Os as either inputs or outputs by writing to the I/O configuration bits. The data for each input or output is kept in the corresponding input or output register. The polarity of the Input Port register can be inverted with the Polarity Inversion register, saving external logic gates. Programmable pull-up and pull-down resistors eliminate the need for discrete components.

The power-on reset puts the registers in their default state and initializes the I²C-bus/SMBus state machine. The RESET pin causes the same reset/initialization to occur without depowering the part. The system controller can also accomplish a reset via an I²C command and initialize all registers to their default state.

The PCAL6524 open-drain interrupt (INT) output is activated when any input state differs from its corresponding Input Port register state. As well, the INT output can be specified to activate on input pin edges. There are a large number of interrupt mask functions available to maximize flexibility.

INT can be connected to the interrupt input of a microcontroller. By sending an interrupt signal on this line, the remote I/O can inform the microcontroller if there is incoming data on its ports without communication via the I²C-bus. Thus, the PCAL6524 can remain a simple target device. The input latch feature holds or latches the input pin state and keeps the logic values that created the interrupt until the controller can service the interrupt. This minimizes the host’s interrupt service response for fast moving inputs.

The device Port P outputs have 25 mA sink capabilities for directly driving LEDs while consuming low device current.

One hardware pin (ADDR) can be used to program and vary the fixed I²C-bus address and allow up to four devices to share the same I²C-bus or SMBus.

Participating products are available for a minimum of 10 years. Designated participating products developed for the automotive, telecom and medical segments are available for a minimum of 15 years.

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Quick reference to our documentation types

9 documents

Compact List

Please wait while your secure files are loading.

1 design file

Receive the full breakdown. See the product footprint and more in the eCad file.

Please wait while your secure files are loading.

1-5 of 9 hardware offerings

Additional hardware available. View our featured partner solutions.

1 hardware offering

To find additional partner offerings that support this product, visit our Partner Marketplace.

1 trainings