Design Files

Receive the full breakdown. See the product footprint and more in the eCad file.

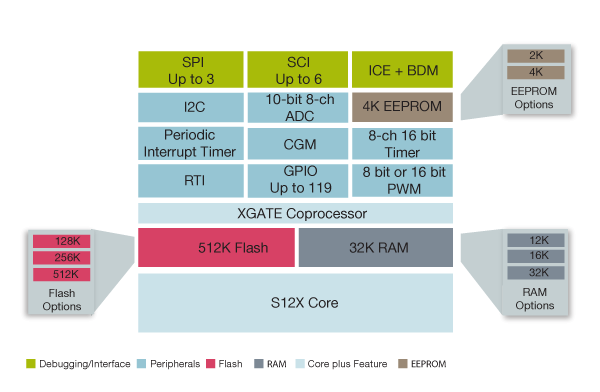

The S12X MCU family retains the cost-effective, power consumption, electromagnetic compatibility and code-size efficiency advantages currently enjoyed by users of the existing 16-bit HCS12 MCU family.

Based on an enhanced HCS12 core, the S12X family gives you two to five times the performance of a 25 MHz HCS12 while retaining a high degree of pin and code compatibility with the HCS12.

The S12X family introduces the performance-boosting XGATE module. Using enhanced DMA functionality, this parallel processing module offloads the CPU by providing high-speed data processing and transfer between peripheral modules, RAM and I/O ports.

Note: To see the product features close this window.

Part numbers include: MC9S12XA256CAA, MC9S12XA256CAG, MC9S12XA256CAL, MC9S12XA256VAA, MC9S12XA256VAL, MC9S12XA512CAA, MC9S12XA512CAG, MC9S12XA512CAL, MC9S12XA512VAA.

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Quick reference to our documentation types.

1-5 of 59 documents

Please wait while your secure files are loading.

Receive the full breakdown. See the product footprint and more in the eCad file.

Receive the full breakdown. See the product footprint and more in the eCad file.

5 hardware offerings

Quick reference to our software types.

5 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

2 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 7 engineering services

.svg)

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.