2.4/5 GHz Dual-Band 2x2 Wi-Fi® 6 (802.11ax) + Bluetooth® 5.3 Automotive Solution

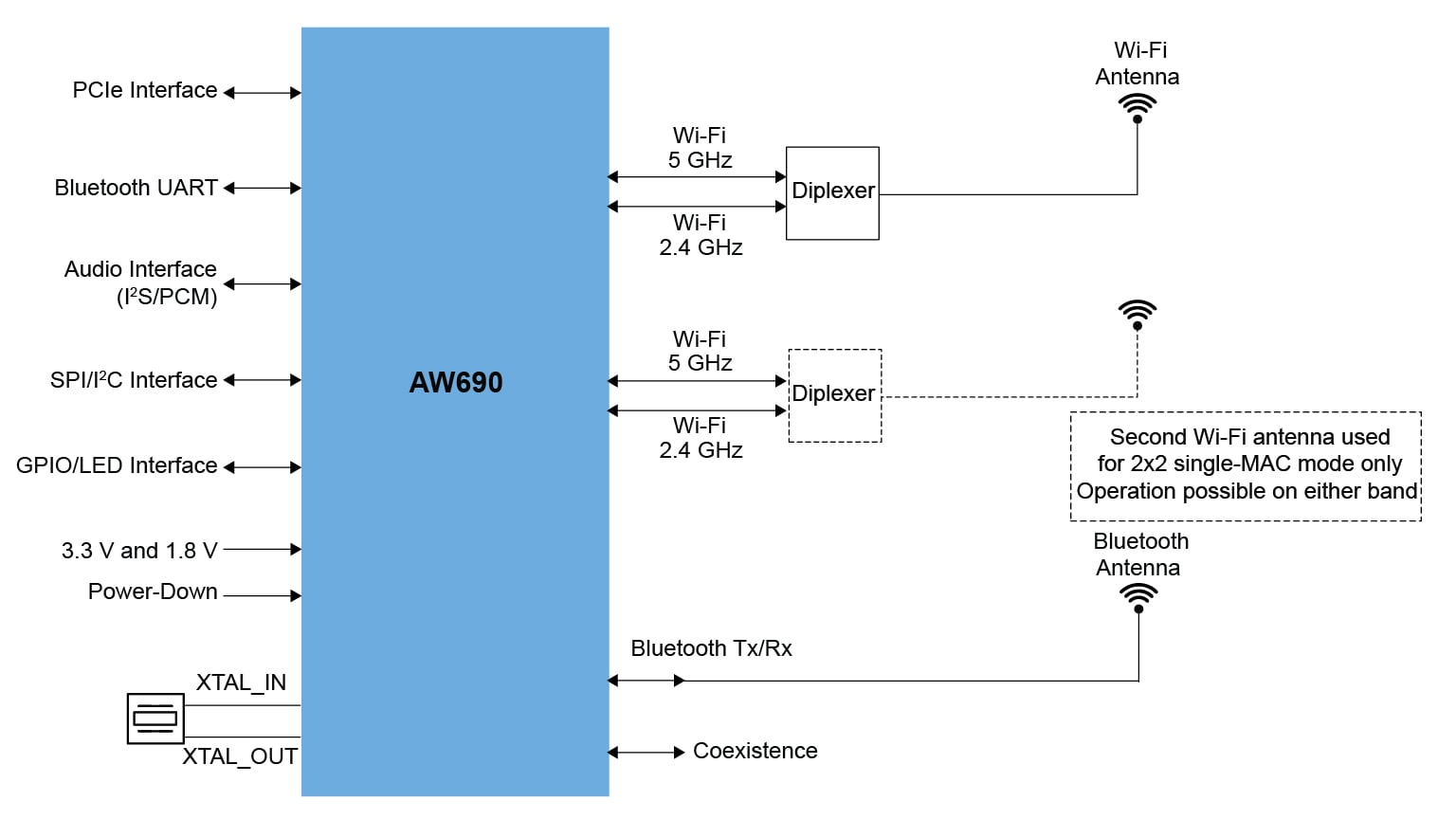

The AW690 is a highly integrated Wi-Fi 6 device enabling concurrent dual Wi-Fi (CDW) and Bluetooth 5.3 operation. Supporting a 1x1 CDW configuration in both the 2.4 GHz and 5 GHz bands, and 2x2 MIMO single-band operation, the system-on-chip (SoC) provides a peak data rate of 1.2 Gbit/s and implements advanced features including MU-MIMO, OFDMA and target wake time (TWT).

With integrated 2.4 GHz and 5 GHz TX power amplifiers (PA), RX low noise amplifiers (LNA) and Tx/Rx switches (T/R SW) as well as a full Bluetooth radio, the AW690 simplifies the design and minimizes the PCB area.

The AW690 implements advanced Wi-Fi and Bluetooth coexistence hardware with algorithms to optimize collaborative performance. In addition, support for external radio coexistence (for example, cellular) is provided through an external interface.

With AEC-Q100 Grade 3- compliant options, the AW690 provides multiple host interface options for the Wi-Fi radios (PCIe) and Bluetooth radio (UART) to provide a flexible design for easy integration into demanding automotive applications.

Wireless modules based on the NXP AW690 are offered by leading module manufacturers.

Choose a diagram:

Note: To see the product features close this window.

| Product | Wi-Fi I/F | Bluetooth I/F | Operating Temp | Antenna Type | Antenna # | Module Type | Module Size | Qualifications | Recommended Host |

|---|---|---|---|---|---|---|---|---|---|

|

JODY-W354-00A |

PCIe | UART, PCM/I²S | -40 to 85 | Antenna pin(s) | 2 | SMD | 13.8 x 19.8 x 2.5 | AEC-Q104; FCC/ISED, RED/UKCA, GITEKI, NCC, KCC, ANZ, BTSIG | i.MX 6/7 |

2.4/5 GHz Dual-Band 2x2 Wi-Fi® 6 (802.11ax) + Bluetooth® 5.3 Automotive Solution

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Quick reference to our documentation types

6 documents

Compact List

Please wait while your secure files are loading.

Please wait while your secure files are loading.

1 hardware offering

To find additional partner offerings that support this product, visit our Partner Marketplace.

Quick reference to our software types.

4 software offerings

Please wait while your secure files are loading.

4 software offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

4 engineering services

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.