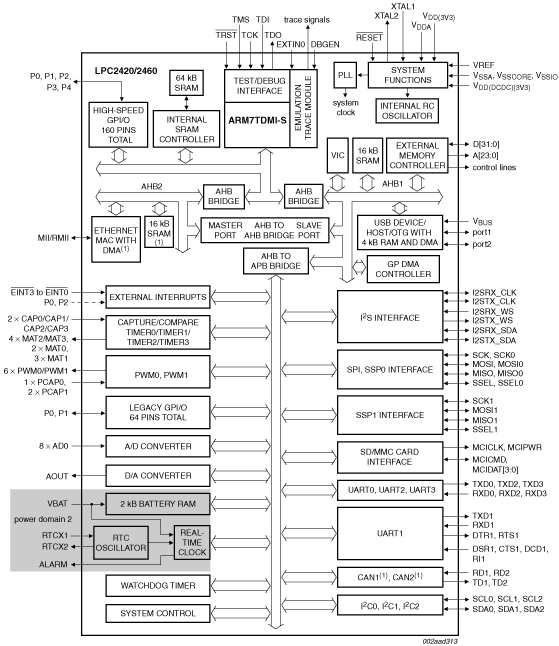

NXP Semiconductors designed the LPC2420/2460 microcontroller around a 16-bit/32-bit Arm7TDMI-S™ CPU core with real-time debug interfaces that include both JTAG and embedded trace. The LPC2420/2460 is flashless. The LPC2420/2460 can execute both 32-bit Arm® and 16-bit Thumb instructions. Support for the two instruction sets means engineers can choose to optimize their application for either performance or code size at the sub-routine level. When the core executes instructions in Thumb state it can reduce code size by more than 30 % with only a small loss in performance while executing instructions in Arm state maximizes core performance.

The LPC2420/2460 microcontroller is ideal for multi-purpose communication applications. It incorporates a 10/100 Ethernet Media Access Controller (MAC) (LPC2460 only), a USB full-speed device/host/OTG controller with 4 kB of endpoint RAM, four UARTs, two Controller Area Network (CAN) channels (LPC2460 only), an SPI interface, two Synchronous Serial Ports (SSP), three I²C interfaces, and an I²S interface. Supporting this collection of serial communications interfaces are the following feature components; an on-chip 4 MHz internal precision oscillator, 82/98 kB of total RAM consisting of 64 kB of local SRAM, 16 kB SRAM for Ethernet (LPC2460 only), 16 kB SRAM for general purpose DMA, 2 kB of battery powered SRAM, and an External Memory Controller (EMC). These features make this device optimally suited for communication gateways and protocol converters. Complementing the many serial communication controllers, versatile clocking capabilities, and memory features are various 32-bit timers, an improved 10-bit ADC, 10-bit DAC, two PWM units, four external interrupt pins, and up to 160 fast GPIO lines. The LPC2420/2460 connects 64 of the GPIO pins to the hardware based Vector Interrupt Controller (VIC) that means these external inputs can generate edge-triggered interrupts. All of these features make the LPC2420/2460 particularly suitable for industrial control and medical systems.