Low-Ohmic Four-Pole Double-Throw Analog Switch

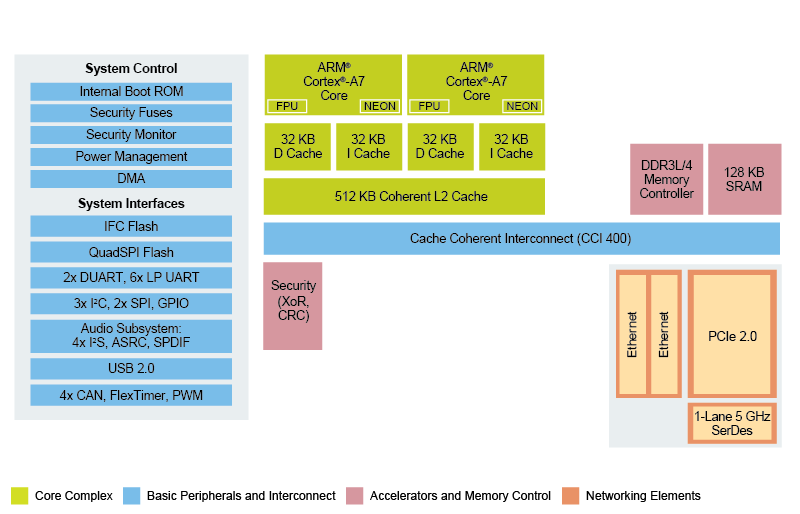

The LS1 family, which includes the LS1020A and LS1022A communications processors, is built on Layerscape architecture, the industry’s first software-aware, core-agnostic networking architecture to offer unprecedented efficiency and scale.

Members of the value-performance tier, the LS1020A and LS1022A processors provide extensive integration and power efficiency for fanless, small form factor enterprise and consumer networking applications. Incorporating dual Arm® Cortex®-A7 cores running up to 1.2 GHz, the LS1020A and LS1022A processors deliver pre-silicon CoreMark® performance of over 7,000, as well as virtualization support, advanced security features and broadest array of high-speed interconnects and optimized peripheral features ever offered in a sub-3 W processor (LS1022A processor is sub-2W typical).

The LS1020A and LS1022A processors features support for multiple industrial protocols, DDR3L/4 running up to 1600 MHz, integrated hardware-based security engine and QUICC Engine®. and ECC protection on both L1 and L2 caches. The LS1020 and LS1022A processors are pin- and software-compatible with the LS1021A processor.

Layerscape processors are part of NXP's EdgeVerse™ edge computing platform.

Choose a diagram:

Note: To see the product features close this window.

Part numbers include: LS1020ASE7HNB, LS1020ASE7KQB, LS1020ASE7MQB, LS1020ASE8KQB, LS1020ASN7HNB, LS1020ASN7KQB, LS1020ASN7MQB, LS1020AXE7HNB, LS1020AXE7KQB, LS1020AXE7MQB, LS1020AXN7HNB, LS1020AXN7KQB, LS1020AXN7MQB, LS1022ASE7EKB, LS1022ASN7EKB, LS1022AXE7EKB, LS1022AXN7EKB.

| LS1021A | LS1020A | LS1022A | |

|---|---|---|---|

| Cores | 2 | 2 | 2 |

| Core Frequency | Up to 1.2 GHz | Up to 1.2 GHz | Up to 600 MHz |

| SerDes | 4 Lanes | 4 Lanes | 1 Lanes |

| Security | SEC 5.4 | SEC 5.4 | SEC 5.4 |

| DDR 4 | Yes | Yes | No |

| USB 3.0 | Yes | Yes | No |

| LCD Support | Yes | No | No |

Select the specifications below to find the perfect fit for your design

| PMIC Part Number | Description | External Memory Voltage (V) | Ambient Operating Temperature (Min-Max) (°C) | Qualification Tier |

|---|---|---|---|---|

| MC34VR500V1ES | Regulator, Buck, Quad with up to 4.5A Output and Triple User-programmable LDOs, QFN 56 | 1.35 | -40 to 105 | Industrial |

| MC34VR500V2ES | Regulator, Buck, Quad with up to 4.5A Output and Factory programmed LDOs, QFN 56 | 1.35 | -40 to 105 | Industrial |

Low-Ohmic Four-Pole Double-Throw Analog Switch

USB PD and Type-C Current-Limited Power Switch

Bidirectional High-Side Power Switch for Charger and USB‑OTG Combined Applications

Dual-Supply Translating Transceiver (Open-Drain, Auto-Direction Sensing)

Bidirectional Voltage Level Translator for Open-Drain and Push-Pull Applications

SMBus-Compatible, 8-Pin, Remote/Local Digital Temperature Sensor

Quick reference to our documentation types.

1-5 of 30 documents

Please wait while your secure files are loading.

3 hardware offerings

1-5 of 11 hardware offerings

.png?imwidth=300)

.png?imwidth=300)

To find additional partner offerings that support this product, visit our Partner Marketplace.

Quick reference to our software types.

2 software files

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

1-5 of 36 software offerings

.svg?imwidth=300)

.svg?imwidth=300)

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 25 engineering services

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

2 trainings

5 trainings

To find additional partner offerings that support this product, visit our Partner Marketplace.