Hardware

5 hardware offerings

-

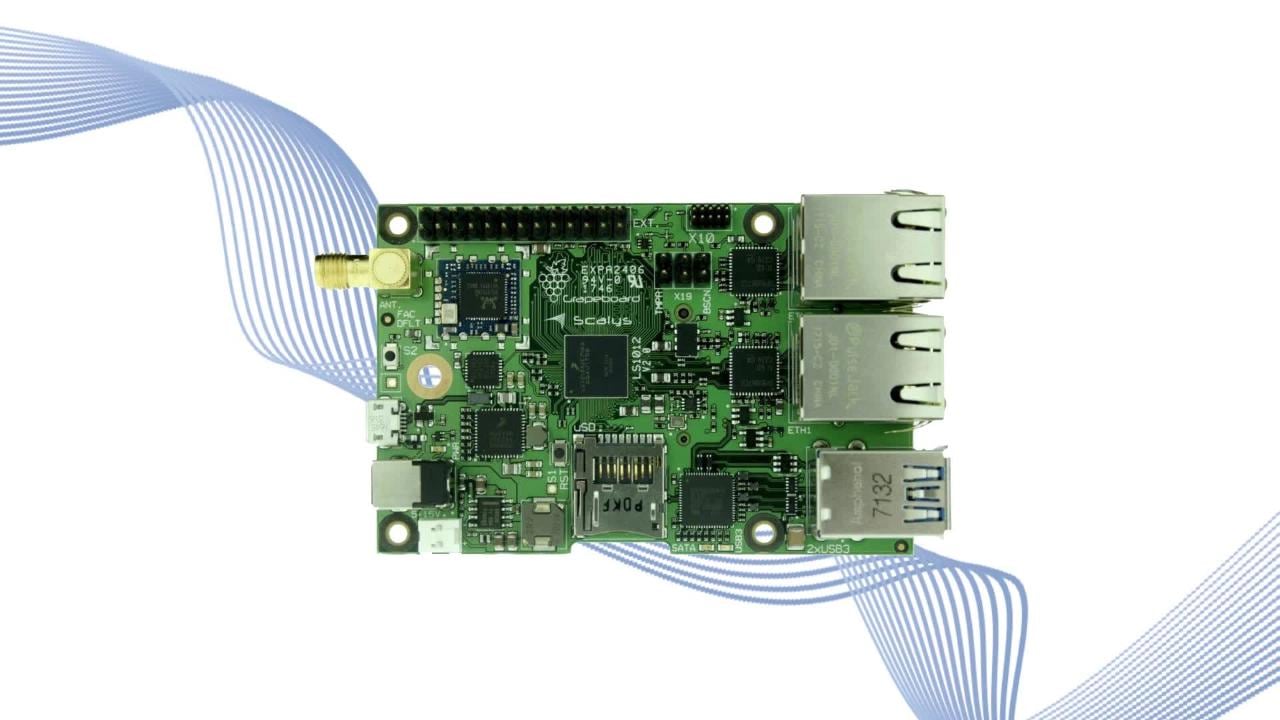

Evaluation and Development Boards

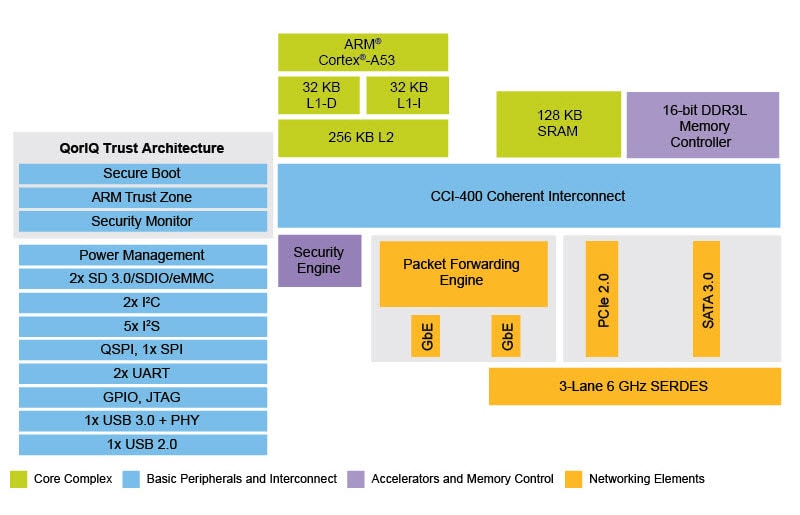

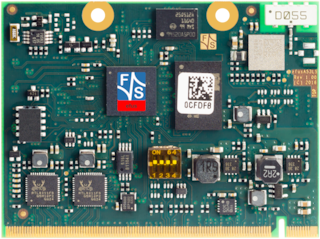

Evaluation and Development BoardsLayerscape FRWY-LS1012A BoardFeatured

-

Evaluation and Development Boards

Evaluation and Development BoardsLayerscape LS1012A Reference Design BoardFeatured

-

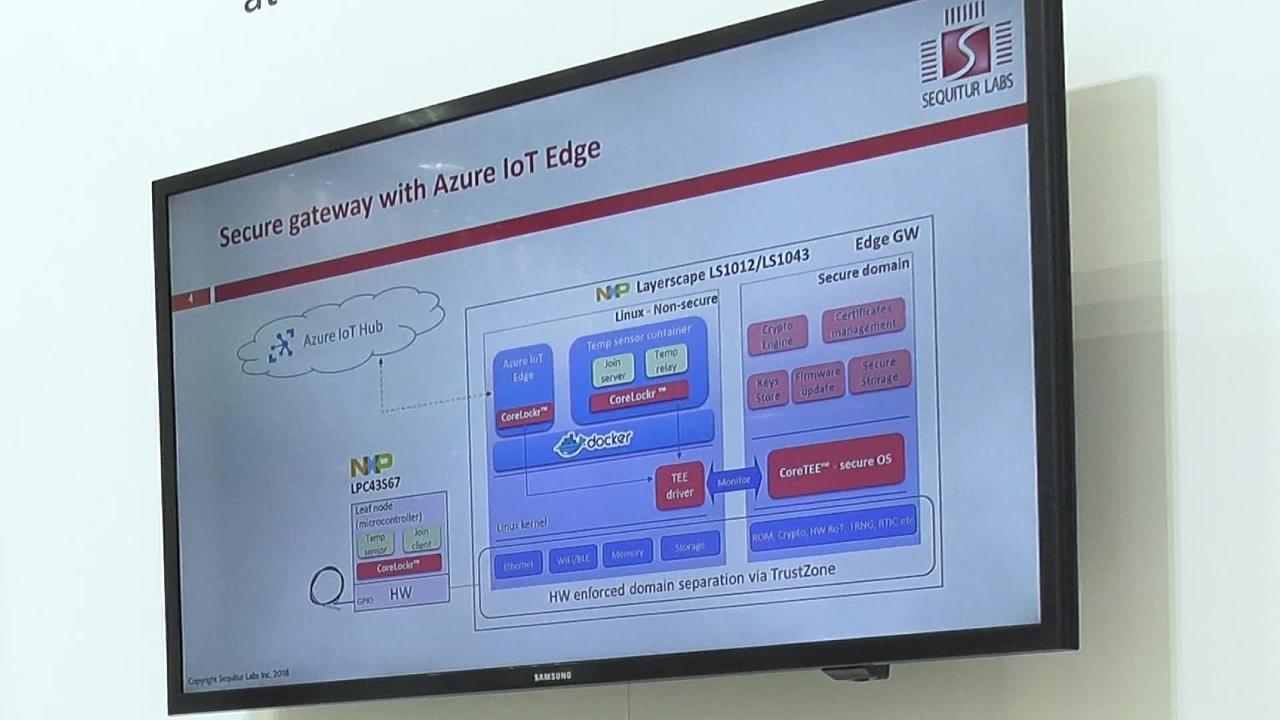

Complete Solution

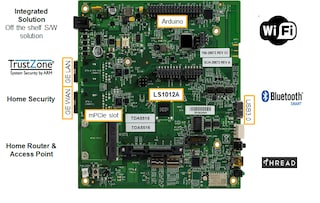

Complete SolutionLayerscape LS1012A Smart Home Gateway Reference Design

-

Additional hardware available. View our featured partner solutions.

-

Emulators, Probes, and Programmers

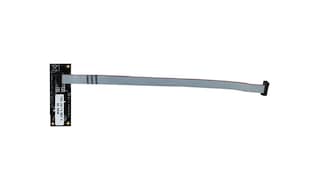

Emulators, Probes, and ProgrammersLS Processor Probe Tips for CodeWarrior TAP

-

Emulators, Probes, and Programmers

Emulators, Probes, and ProgrammersCodeWarrior® TAP