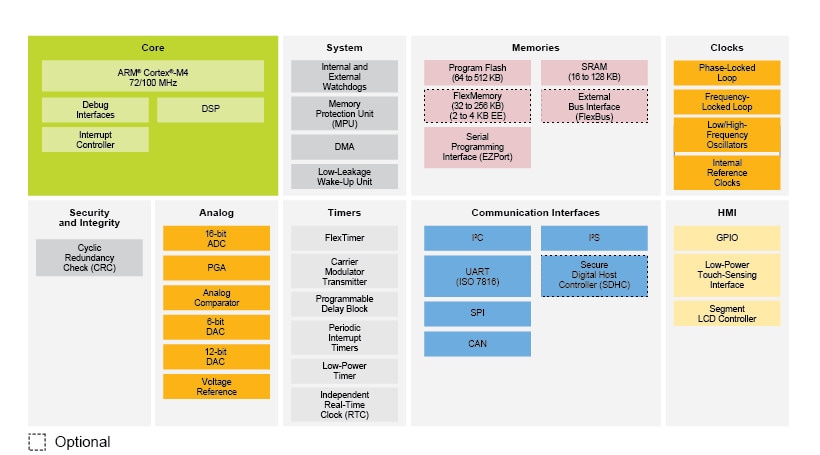

Kinetis® K40-72 MHz, Mixed-Signal Integration Microcontrollers based on Arm® Cortex®-M4 Core

The Kinetis® K30 100 MHz Segment LCD MCUs are built on the Arm® Cortex®-M4 core and feature advanced analog integration and serial communication. This family shares the comprehensive enablement and scalability of the Kinetis portfolio.

Note: To see the product features close this window.

Part numbers include: MK30DN512VLL10, MK30DN512VLQ10, MK30DN512ZVLK10, MK30DN512ZVLQ10, MK30DX256VLQ10, MK30DX256ZVLQ10.

Quick reference to our documentation types.

1-5 of 92 documents

Please wait while your secure files are loading.

2 design files

Please wait while your secure files are loading.

1-5 of 11 hardware offerings

Additional hardware available. View our featured partner solutions.

1-5 of 29 hardware offerings

To find additional partner offerings that support this product, visit our Partner Marketplace.

Quick reference to our software types.

1-5 of 17 software files

Additional software available. View our featured partner solutions.

Note: For better experience, software downloads are recommended on desktop.

Please wait while your secure files are loading.

1-5 of 51 software offerings

.svg?imwidth=300)

.svg?imwidth=300)

To find additional partner offerings that support this product, visit our Partner Marketplace.

1-5 of 18 engineering services

.svg)

There are no results for this selection.

To find additional partner offerings that support this product, visit our Partner Marketplace.

4 trainings

Additional trainings are available. View our featured partner trainings.

8 trainings

To find additional partner offerings that support this product, visit our Partner Marketplace.